# HD64645/HD64646

# LCTC (LCD Timing Controller)

# HITACHI

ADE-207-276(Z) '99.9 Rev. 0.0

### Description

The HD64645/HD64646 LCTC is a control LSI for large size dot matrix liquid crystal displays. The LCTC is software compatible with the HD6845 CRTC, since its programming method of internal registers and memory addresses is based on the CRTC. A display system can be easily converted from a CRT to an LCD.

The HD64646 LCTC is a modified version of the HD64645 LCTC with different LCD interface timing.

The LCTC offers a variety of functions and performance features such as vertical and horizontal scrolling, and various types of character attribute functions such as reverse video, blinking, nondisplay (white or black), and an OR function for simple superimposition of character and graphic displays. The LCTC also provides DRAM refresh address output.

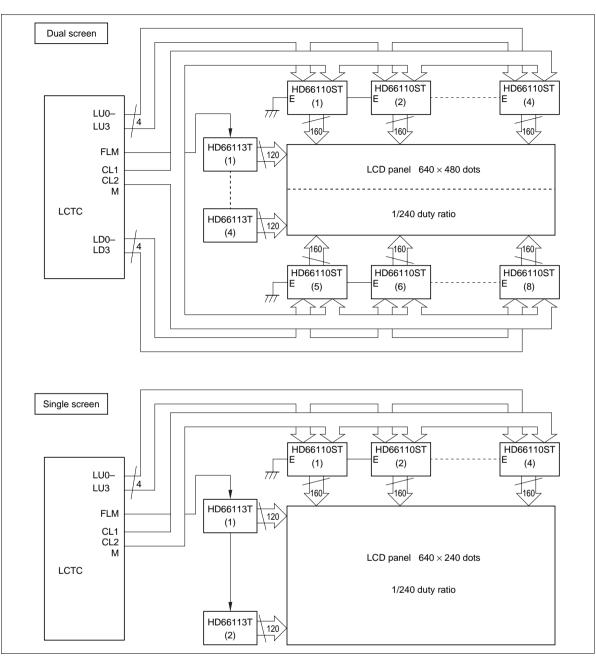

A compact LCD system with a large screen can be configured by connecting the LCTC with the HD66110ST (column driver) and the HD66113T (common driver) by utilizing 4-bit  $\times$  2 data outputs. Power dissipation has been lowered by adopting the CMOS process.

### Features

- Software compatible with the HD6845 CRTC

- Programmable screen size

- Up to 1024 dots (height)

- Up to 4096 dots (width)

- High-speed data transfer

- Up to 20 Mbits/s in character mode

- Up to 40 Mbits/s in graphic mode

- Selectable single or dual screen configuration

- Programmable multiplexing duty ratio: static to 1/512 duty cycle

- Programmable character font

- 1-32 dots (height)

- 8 dots (width)

- Versatile character attributes: reverse video, blinking, nondisplay (white), nondisplay (black)

- OR function: superimposing characters and graphics display

- Cursor with programmable height, blink rate, display position, and on/off switch

- Vertical Smooth Scrolling and horizontal scrolling by the character

- Versatile display modes programmable by mode register or external pins: display on/off, graphic or character, normal or wide, attributes, and blink enable

- Refresh address output for dynamic RAM

- 4- or 8-bit parallel data transfer between LCTC and LCD driver

- Recommended LCD driver

- HD66110ST and HD66120 (segment)

- HD66113T and HD66115T (common)

- CPU interface

- 80 family

- CMOS process

- Single +5 V  $\pm 10\%$

### **Ordering Information**

| Type No.  | Package                     |

|-----------|-----------------------------|

| HD64645F  | 80-pin plastic QFP (FP-80)  |

| HD64646FS | 80-pin plastic QFP (FP-80B) |

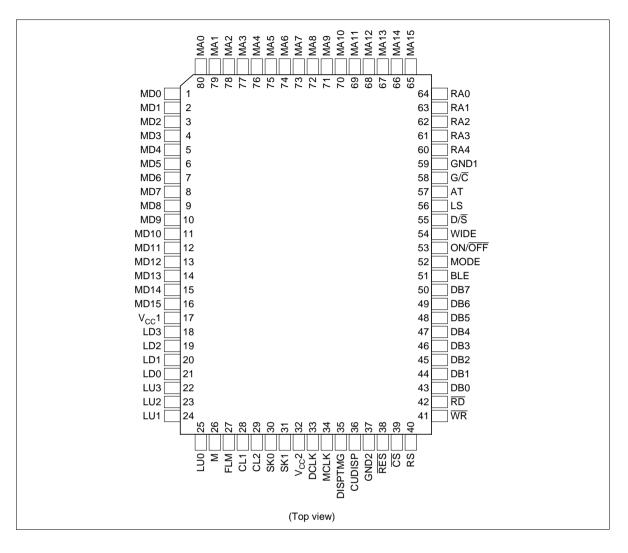

### **Pin Arrangement**

# **Pin Description**

| Symbol                               | Pin Number | I/O | Name                    |

|--------------------------------------|------------|-----|-------------------------|

| V <sub>cc</sub> 1, V <sub>cc</sub> 2 | 17, 32     | —   | V <sub>cc</sub>         |

| GND1, GND2                           | 37, 59     | _   | Ground                  |

| LU0–LU3                              | 22–25      | 0   | LCD up panel data 0–3   |

| LD0–LD3                              | 18–21      | 0   | LCD down panel data 0–3 |

| CL1                                  | 28         | 0   | Clock one               |

| CL2                                  | 29         | 0   | Clock two               |

| FLM                                  | 27         | 0   | First line marker       |

| Μ                                    | 26         | 0   | Μ                       |

| MA0–MA15                             | 65–80      | 0   | Memory address 0–15     |

| RA0–RA4                              | 60–64      | 0   | Raster address 0–4      |

| MD0-MD7                              | 1–8        | I   | Memory Data 0–7         |

| MD8–MD15                             | 9–16       | I   | Memory Data 8–15        |

| DB0–DB7                              | 43–50      | I/O | Data bus 0–7            |

| CS                                   | 39         | Ι   | Chip select             |

| WR                                   | 41         | I   | Write                   |

| RD                                   | 42         | I   | Read                    |

| RS                                   | 40         | I   | Register select         |

| RES                                  | 38         | I   | Reset                   |

| DCLK                                 | 33         | I   | D clock                 |

| MCLK                                 | 34         | 0   | M clock                 |

| DISPTMG                              | 35         | 0   | Display timing          |

| CUDISP                               | 36         | 0   | Cursor display          |

| SK0                                  | 30         | I   | Skew 0                  |

| SK1                                  | 31         | I   | Skew 1                  |

| ON/OFF                               | 53         | I   | On/off                  |

| BLE                                  | 51         | I   | Blink enable            |

| AT                                   | 57         | I   | Attribute               |

| G/C                                  | 58         | I   | Graphic/character       |

| WIDE                                 | 54         | Ι   | Wide                    |

| LS                                   | 56         | I   | Large screen            |

| D/S                                  | 55         | I   | Dual/single             |

| MODE                                 | 52         | Ι   | Mode                    |

### **Pin Functions**

Power Supply (V<sub>CC</sub>1, V<sub>CC</sub>2, GND)

Power Supply Pin (+5 V): Connect  $V_{cc}1$  and  $V_{cc}2$  with +5V power supply circuit.

Ground Pin (0 V): Connect GND1 and GND2 with 0V.

#### LCD Interface

LCD Up Panel Data (LU0–LU3), LCD Down Panel Data (LD0–LD3): LU0–LU3 and LD0–LD3 output LCD data as shown in Table 1.

Clock One (CL1): CL1 supplies timing clocks for display data latch.

Clock Two (CL2): CL2 supplies timing clock for display data shift.

First Line Marker (FLM): FLM supplies first line marker.

M (M): M converts liquid crystal drive output to AC.

#### **Memory Interface**

Memory Address (MA0–MA15): MA0–MA15 supply the display memory address.

Raster Address (RA0-RA4): RA0-RA4 supply the raster address.

Memory Data (MD0–MD7): MD0–MD7 receive the character dot data or bit-mapped data.

Memory Data (MD8–MD15): MD8–MD15 receive attribute code data or bit-mapped data.

#### **MPU Interface**

Data Bus (DB0–DB7): DB0–DB7 send/receive data as a three-state I/O common bus.

Chip Select ( $\overline{CS}$ ):  $\overline{CS}$  selects a chip. Low level enables MPU read/write of the LCTC internal registers.

Write ( $\overline{WR}$ ):  $\overline{WR}$  receives MPU write strobe.

**Read** ( $\overline{RD}$ ):  $\overline{RD}$  receives MPU read strobe.

Register Select (RS): RS selects registers. (Refer to Table 4.)

**Reset** ( $\overline{\text{RES}}$ ):  $\overline{\text{RES}}$  performs external reset of the LCTC. Low level of  $\overline{\text{RES}}$  stops and zero-clears the LCTC internal counter. No register contents are affected.

Timing Signal

**D** Clock (**DCLK**): DCLK inputs the system clock.

M Clock (MCLK): MCLK indicates memory cycle; DCLK is divided by four.

**Display Timing (DISPTMG):** DISPTMG high indicates that the LCTC is reading display data.

Cursor Display (CUDISP): CUDISP supplies cursor display timing; connect with MD12 in character mode.

Skew 0 (SK0)/Skew 1 (SK1): SK0 and SK1 control skew timing. Refer to Table 2.

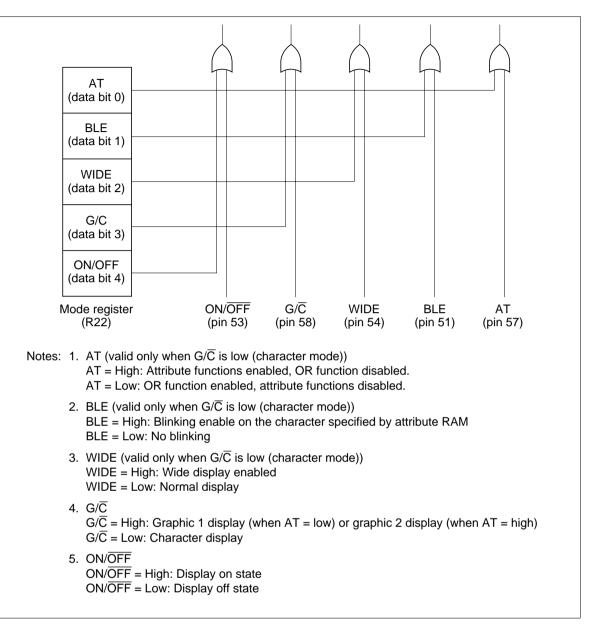

### Mode Select

The mode select pins  $ON/\overline{OFF}$ , BLE, AT,  $G/\overline{C}$ , and WIDE are ORed with the mode register (R22) to determine the mode.

**On/Off (ON/\overline{OFF}):** ON/ $\overline{OFF}$  switches display on and off (high = display on).

**Blink Enable (BLE):** BLE high level enables attribute code "blinking" (MD13) and provides normal/blank blinking of specified characters for 32 frames each.

Attribute (AT): AT controls character attribute functions.

**Graphic/Character** ( $G/\overline{C}$ ):  $G/\overline{C}$  switches between graphic and character display mode (graphic display when high).

**Wide (WIDE):** WIDE switches between normal and wide display mode (high = wide display, low = normal display).

**Large Screen (LS):** LS controls a large screen. LS high provides a data transfer rate of 40 Mbits/s for a graphic display. Also used to specify 8-bit LCD interface mode. For more details, refer to Table 10.

**Dual/Single** ( $D/\overline{S}$ ):  $D/\overline{S}$  switches between single and dual screen display (dual screen display when high).

**Mode** (**MODE**): MODE controls easy mode. MODE high sets duty ratio, maximum number of rasters, cursor start/end rasters, etc. (Refer to Table 8.)

### Table 1 LCD Up Panel Data and LCD Down Panel Data

|          | S            | Single Screen |                              |

|----------|--------------|---------------|------------------------------|

| Pin Name | 4-Bit Data   | 8-Bit Data    | Dual Screen                  |

| LU0–LU3  | Data output  | Data output   | Data output for upper screen |

| LD0–LD3  | Disconnected | Data output   | Data output for lower screen |

| SK0SK1Skew Function00No skew101-character time skew012-character time skew11Prohibited combination | Table 2 | Skew Sig | nals                   |

|----------------------------------------------------------------------------------------------------|---------|----------|------------------------|

| 1     0     1-character time skew       0     1     2-character time skew                          | SK0     | SK1      | Skew Function          |

| 0 1 2-character time skew                                                                          | 0       | 0        | No skew                |

|                                                                                                    | 1       | 0        | 1-character time skew  |

| 1 1 Prohibited combination                                                                         | 0       | 1        | 2-character time skew  |

|                                                                                                    | 1       | 1        | Prohibited combination |

### **Function Overview**

#### Main Features of HD64645/HD64646

Main features of the LCTC are:

- High-resolution liquid crystal display screen control (up to  $720 \times 512$  dots)

- Software compatible with HD6845 (CRTC)

- Built-in character attribute control circuit

Table 3 shows how the LCTC can be used.

| Classification | ltem                           | Description                                                                                                                                                                                                                                |

|----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functions      | Screen format                  | <ul> <li>Programmable horizontal scanning cycle by the character clock period</li> <li>Programmable multiplexing duty ratio from static up to 1/512</li> </ul>                                                                             |

|                |                                | <ul> <li>Programmable number of vertical displayed characters</li> <li>Programmable number of rasters per character row<br/>(number of vertical dots within a character row + space<br/>between character rows)</li> </ul>                 |

|                | Cursor control                 | <ul> <li>Programmable cursor display position, corresponding to<br/>RAM address</li> <li>Programmable cursor height by setting display start/end<br/>rasters</li> </ul>                                                                    |

|                | Memory rewriting               | <ul> <li>Programmable blink rate, 1/32 or 1/64 frame rate</li> <li>Time for rewriting memory set either by specifying number<br/>of horizontal total characters or by cycle steal utilizing<br/>MCLK</li> </ul>                            |

|                | Memory addressing              | <ul> <li>16-bit memory address output, up to 64 kbytes × 2<br/>memory accessible</li> <li>DRAM refresh address output</li> </ul>                                                                                                           |

|                | Paging and scrolling           | <ul> <li>Paging by updating start address</li> <li>Horizontal scrolling by the character, by setting horizontal virtual screen width</li> <li>Vertical smooth scrolling by updating display start raster</li> </ul>                        |

|                | Character attributes           | Reverse video, blinking, nondisplay (white or black),<br>display ON/OFF                                                                                                                                                                    |

| Application    | CRTC compatible<br>OR function | <ul> <li>Facilitates system replacement of CRT display with LCD</li> <li>Enables superimposing display of character screen and graphic screen</li> </ul>                                                                                   |

| Configuration  | LCTC configuration             | <ul> <li>Single 5 V power supply</li> <li>I/O TTL compatible except RES, MODE, SK0, SK1</li> <li>Bus connectable with 80 family</li> <li>CMOS process</li> <li>Internal logic fully static</li> <li>80-pin flat plastic package</li> </ul> |

### Table 3Functions, Application, and Configuration

### Differences between HD64645 and HD64646

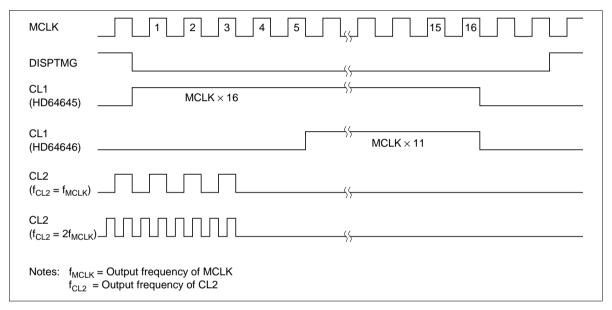

Figure 1 and Figure 2 show the relation between display data transfer period, when display data shift clock CL2 changes, and display data latch clock CL1. Figure 1 shows the case without skew function and Figure 2 shows the case with skew function.

In Figure 1, high period between CL2 and CL1 of HD64645 overlap. HD64646 has no overlap like HD64645, and except for this overlap, HD64646 is the same as HD64645 functionally.

Also for the skew function, phase relation between CL1 and CL2 changes. As Figure 2 shows, data transfer period and CL1 high period of HD64646 never overlap with the skew function.

Figure 1 Differences between HD64645 and HD64646 (No Skew)

| MCLK 1 2 3 4 5 15 16                           |

|------------------------------------------------|

| DISPTMG                                        |

| CL1 (HD64645) MCLK × 16                        |

| CL1<br>(HD64646) MCLK × 11                     |

| CL2<br>(f <sub>CL2</sub> = f <sub>MCLK</sub> ) |

| $CL2 (f_{CL2} = 2f_{MCLK}) $                   |

| 1 Character Skew                               |

| MCLK123451516                                  |

| DISPTMG                                        |

| CL1<br>(HD64645) MCLK × 16                     |

|                                                |

| CL1<br>(HD64646) MCLK × 11                     |

|                                                |

| (HD64646) ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,    |

Figure 2 Differences between HD64645 and HD64646 (Skew)

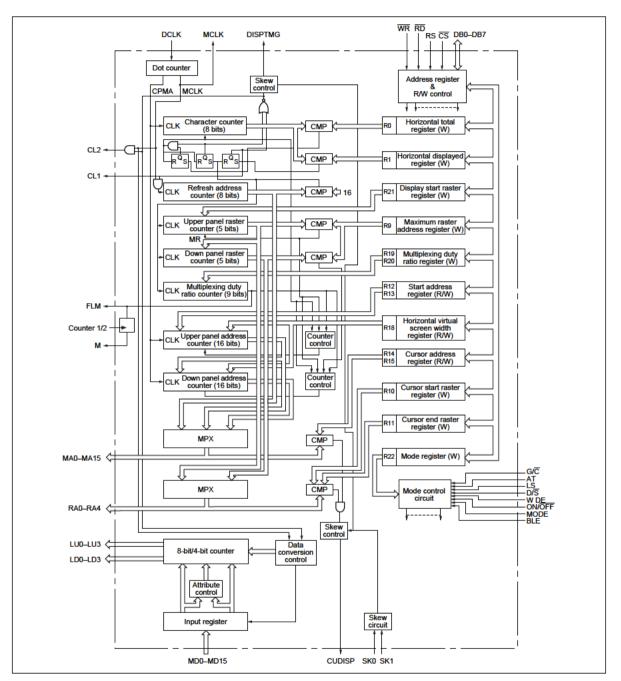

### **Internal Block Diagram**

Figure 3 is a block diagram of the LCTC.

Figure 3 LCTC Block Diagram

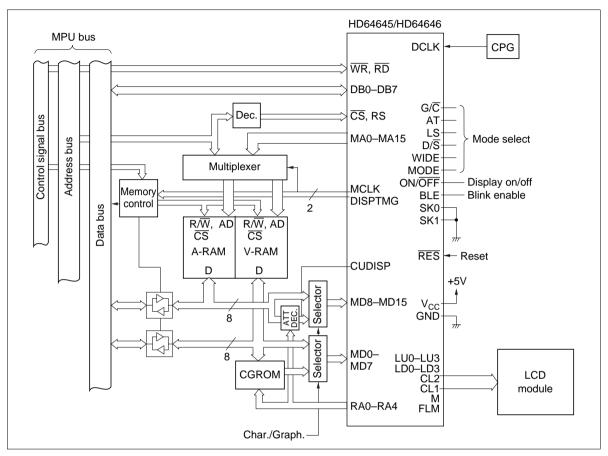

### **System Block Configuration Examples**

Figure 4 is a block diagram of a character/graphic display system. Figure 6 shows two examples using LCD drivers.

Figure 4 Character/Graphic Display System Example

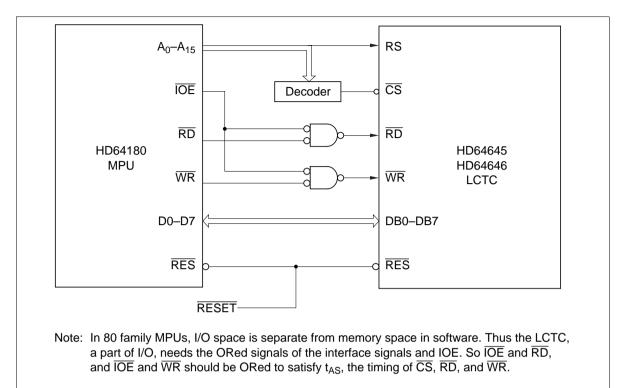

### Interface to MPU

#### Interface between HD64180, HD64645 and HD64646

Figure 5 Interfacep to MPU

Figure 6 LCD Driver Examples

### Registers

Table 4 shows the register mapping. Table 5 describes their function. Table 6 shows the differences between CRTC and LCTC registers.

### Table 4Registers Mapping

|    |    | Address<br>Register | Reg. |                                 |                |        |     |   |   |   | Data       | a Bit |      |     |    |

|----|----|---------------------|------|---------------------------------|----------------|--------|-----|---|---|---|------------|-------|------|-----|----|

| CS | RS | 4 3 2 1 0           | No.  | Register Name                   | Program Unit   | Symbol | R/W | 7 | 6 | 5 | 4          | 3     | 2    | 1   | 0  |

| 1  | —  |                     |      | Invalid                         | _              | —      | —   |   |   |   |            |       |      |     |    |

| 0  | 0  |                     | AR   | Address Register                | _              | —      | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 0 0 0 0 0           | R0   | Horizontal total characters     | Character*3    | Nht    | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 00001               | R1   | Horizontal displayed char.s     | Character      | Nhd    | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 01001               | R9   | Maximum raster address          | Raster         | Nr     | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 0 1 0 1 0           | R10  | Cursor start raster             | Raster*4       | Ncs    | W   |   | В | Ρ |            |       |      |     |    |

| 0  | 1  | 0 1 0 1 1           | R11  | Cursor end raster               | Raster         | Nce    | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 0 1 1 0 0           | R12  | Start address (H)               | Memory address | _      | R/W |   |   |   |            |       |      |     |    |

| 0  | 1  | 0 1 1 0 1           | R13  | Start address (L)               | Memory address | _      | R/W |   |   |   |            |       |      |     |    |

| 0  | 1  | 0 1 1 1 0           | R14  | Cursor address (H)              | Memory address | _      | R/W |   |   |   |            |       |      |     |    |

| 0  | 1  | 0 1 1 1 1           | R15  | Cursor address (L)              | Memory address | _      | R/W |   |   |   |            |       |      |     |    |

| 0  | 1  | 10010               | R18  | Horizontal virtual screen width | Character      | Nir    | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 10011               | R19  | Multiplexing duty ratio (H)     | Raster*3       | Ndh    | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 10100               | R20  | Multiplexing duty ratio (L)     | Raster*3       | Ndl    | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 10101               | R21  | Display start raster            | Raster         | Nsr    | W   |   |   |   |            |       |      |     |    |

| 0  | 1  | 10110               | R22  | Mode register                   | <u>*</u> *5    | —      | W   |   |   |   | ON/<br>OFF | G/C   | WIDE | BLE | AT |

Notes: 1. : Invalid data bits

- 2. R/W indicates whether write access or read access is enabled to/from each register.

- W: Only write accessible

R/W: Both read and write accessible

- 3. The "value to be specified minus 1" should be programmed in these registers: R0, R1 and R20.

- 4. Data bits 5 and 6 of cursor start register control the cursor status as shown below (for more details, refer to page 27).

| В | Ρ | Cursor Blink Mode             |

|---|---|-------------------------------|

| 0 | 0 | Cursor on; without blinking   |

| 0 | 1 | Cursor off                    |

| 1 | 0 | Blinking once every 32 frames |

| 1 | 1 | Blinking once every 64 frames |

5. The OR of mode pin status and mode register data determines the mode.

Registers R2–R8, R16, and R17 are not assigned for the LCTC. Programming to these registers will be ignored.

| Reg. No.   | Register Name                                              | Size (Bits) | Description                                                                                         |

|------------|------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------|

| AR         | Address register                                           | 5           | Specifies the internal control registers<br>(R0, R1, R9–R15, R18–R22) address to<br>be accessed     |

| R0         | Horizontal total characters                                | 8           | Specifies the horizontal scanning period                                                            |

| R1         | Horizontal displayed characters                            | 8           | Specifies the number of displayed characters per character row                                      |

| R9         | Maximum raster address                                     | 5           | Specifies the number of rasters per<br>character row, including the space<br>between character rows |

| R10        | Cursor start raster                                        | 5 + 2       | Specifies the cursor start raster address and its blink mode                                        |

| R11        | Cursor end raster                                          | 5           | Specifies the cursor end raster address                                                             |

| R12<br>R13 | Start address (H)<br>Start address (L)                     | 16          | Specify the display start address                                                                   |

| R14<br>R15 | Cursor address (H)<br>Cursor address (L)                   | 16          | Specify the cursor display address                                                                  |

| R18        | Horizontal virtual screen width                            | 8           | Specifies the length of one row in memory space for horizontal scrolling                            |

| R19<br>R20 | Multiplexing duty ratio (H)<br>Multiplexing duty ratio (L) | 9           | Specify the number of rasters for one screen                                                        |

| R21        | Display start raster                                       | 5           | Specifies the display start raster within a character row for smooth scrolling                      |

| R22        | Mode register                                              | 5           | Controls the display mode                                                                           |

Table 5Internal Register Description

Note: For more details of registers, refer to "Internal Registers."

| Reg. No. | LCTC HD64645/HD64646            | Comparison           | CRTC HD6845                     |

|----------|---------------------------------|----------------------|---------------------------------|

| AR       | Address register                | Equivalent to CRTC   | Address register                |

| R0       | Horizontal total characters     |                      | Horizontal total characters     |

| R1       | Horizontal displayed characters |                      | Horizontal displayed characters |

| R2       | —                               | Particular to CRTC;  | Horizontal sync position        |

| R3       |                                 | unnecessary for LCTC | Sync width                      |

| R4       |                                 |                      | Vertical total characters       |

| R5       |                                 |                      | Vertical total adjust           |

| R6       |                                 |                      | Vertical displayed characters   |

| R7       |                                 |                      | Vertical sync position          |

| R8       |                                 |                      | Interface and skew              |

| R9       | Maximum raster address          | Equivalent to CRTC   | Maximum raster address          |

| R10      | Cursor start raster             |                      | Cursor start raster             |

| R11      | Cursor end raster               |                      | Cursor end raster               |

| R12      | Start address (H)               |                      | Start address (H)               |

| R13      | Start address (L)               |                      | Start address (L)               |

| R14      | Cursor address (H)              |                      | Cursor (H)                      |

| R15      | Cursor address (L)              |                      | Cursor (L)                      |

| R16      |                                 | Particular to CRTC;  | Light pen (H)                   |

| R17      |                                 | unnecessary for LCTC | Light pen (L)                   |

| R18      | Horizontal virtual screen width | Additional registers |                                 |

| R19      | Multiplexing duty ratio (H)     | for LCTC             |                                 |

| R20      | Multiplexing duty ratio (L)     |                      |                                 |

| R21      | Display start raster            |                      |                                 |

| R22      | Mode register                   |                      |                                 |

Internal Register Comparison between LCTC and CRTC

Table 6

### **Functional Description**

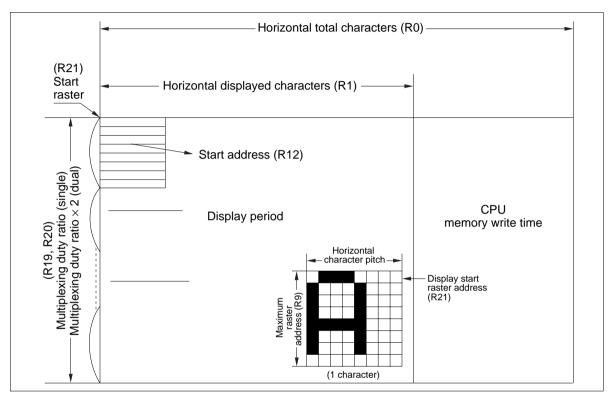

### **Programmable Screen Format**

Figure 7 illustrates the relation between LCD display screen and registers. Figure 8 shows a timing chart of signals output from the LCTC in mode 5 as an example.

Figure 7 Relation between Display Screen and Registers

|                     | 7                                   |                                                               |             |

|---------------------|-------------------------------------|---------------------------------------------------------------|-------------|

| (Latch<br>timing) — | Ŋ.N.N.N                             |                                                               |             |

| MA0-MA15            | €<br>0 1 2 3 4 5 Nind-4 Nind-3 Nind | 2/Nhd-1/Ref-1/Ref-2/Ref-3/Ref-4//Ref-14/Ref-15/Ref-16//Nht-2/ | iht-1 Nht X |

| RA0–RA4             |                                     | X                                                             |             |

| FLM                 |                                     | MCLK × 16                                                     |             |

| M                   |                                     | X                                                             |             |

| CL1                 |                                     | MCLK × 16                                                     |             |

| CL2                 |                                     |                                                               |             |

| LU0                 | 001112233344455                     |                                                               | XX          |

| LU1                 | YOYOY1Y1Y2Y2Y3Y3Y4Y4Y5Y5Y           |                                                               | XX          |

| LU2                 | 00011122333244455                   |                                                               | XX          |

| LU3                 | <u>\0\0\1\1\2\2\3\3\4\4\5\5\</u>    |                                                               | XX          |

| LD0                 |                                     |                                                               | XX          |

| LD1                 | XXXXXXXXXXX                         |                                                               | XX          |

| LD2                 |                                     |                                                               | XX          |

| LD3                 |                                     |                                                               | χχ          |

Figure 8 LCTC Timing Chart (In Mode 5: Single Screen, 4-Bit Transfer, Normal Character Display)

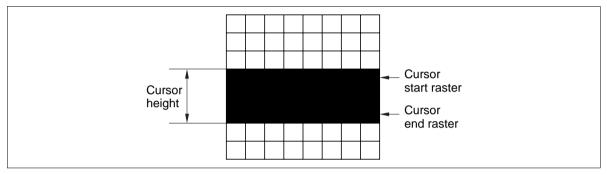

### **Cursor Control**

The following cursor functions (Figure 9) can be controlled by programming specific registers.

- Cursor display position

- Cursor height

- Cursor blink mode

A cursor can be displayed only in character mode. Also, CUDISP pin must be connected to MD12 pin to display a cursor.

Figure 9 Cursor Display

### **Character Mode and Graphic Mode**

The LCTC supports two types of display modes; character mode and graphic mode. Graphic mode 2 is provided to utilize software for a system using the CRTC (HD6845).

The display mode is controlled by an OR between the mode select pins ( $D/\overline{S}$ ,  $G/\overline{C}$ , LS, WIDE, AT) and mode register (R22).

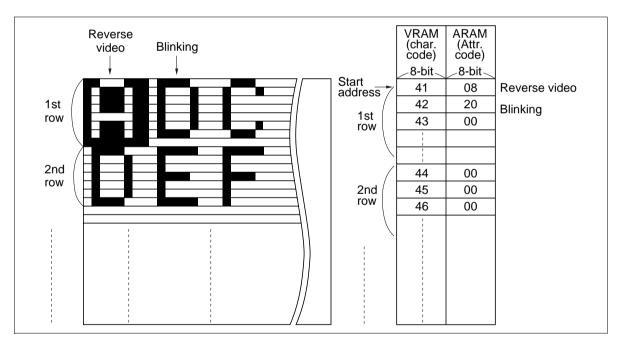

**Character Mode:** character mode displays characters by using CG-ROM. The display data supplied from memory is accessed in 8-bit units. A variety of character attribute functions are provided, such as reverse video, blinking, nondisplay (white or black), by storing the attribute data in attribute RAM (A-RAM).

Figure 10 illustrates the relation between character display screen and memory contents.

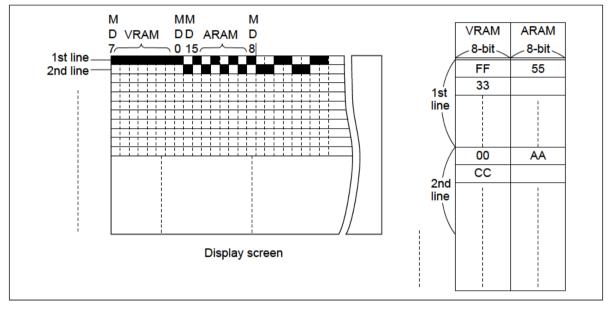

**Graphic Mode 1:** Graphic mode 1 directly displays data stored in a graphic memory buffer. The display data supplied from memory is accessed in 16-bit units. Character attribute functions or wide mode are not provided. Figure 11 illustrates the relation between graphic display screen and memory contents.

**Graphic Mode 2:** Graphic mode 2 utilizes software for a system using the CRTC (HD6845). The display data supplied from memory is accessed in 16-bit units. Character attribute functions or wide mode are not provided. The same memory addresses are output repeatedly the number of times specified by maximum raster register (R9). The raster address is output in the same way as in character mode.

Figure 10 Relation between Character Screen and Memory Contents

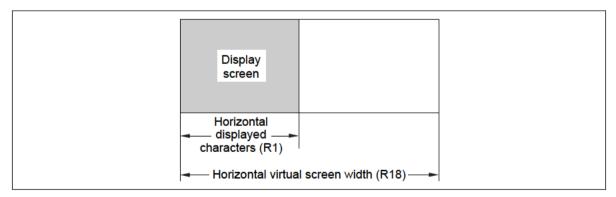

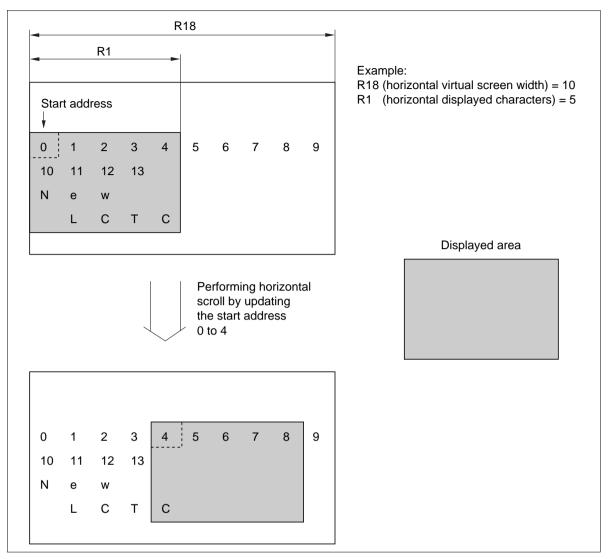

### Horizontal Virtual Screen Width

Horizontal virtual screen width can be specified by the character in addition to the number of horizontal displayed characters (Figure 12).

The display screen can be scrolled in any direction by the character, by setting the horizontal virtual screen width and updating the start address. This function is enabled by programming the horizontal virtual screen width register (R18).

Figure 13 shows an example.

Figure 11 Relation between Graphic Screen and Memory Contents

Figure 12 Horizontal Virtual Screen Width

Figure 13 Example of Horizontal Scroll by Setting Horizontal Virtual Screen Width

### Smooth Scroll

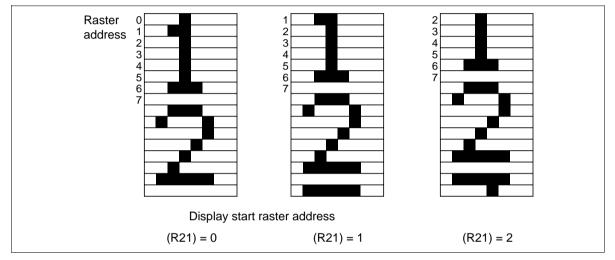

Vertical smooth scrolling (Figure 14) is performed by updating the display start raster, as specified by the start raster register (R21). This function is offered only in character mode.

### Wide Display

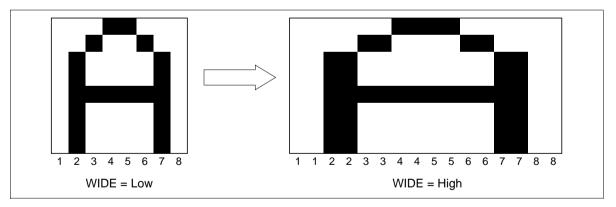

The character to be displayed can be doubled in width, by supplying the same data twice (Figure 15). This function is offered only in character mode, and controlled either by bit 2 of the mode register (R22) or by the WIDE pin.

Figure 14 Example of Smooth Scroll by Setting Display Start Raster Address

Figure 15 Example of Wide Display

#### Attribute Functions

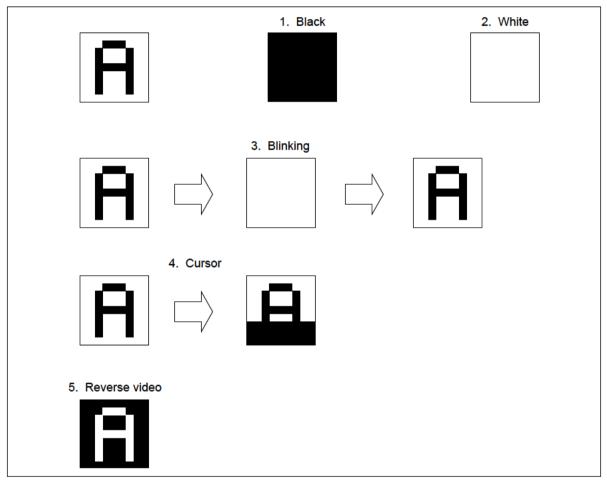

A variety of character attribute functions such as reverse video, blinking, nondisplay (white) or nondisplay (black) can be implemented by storing the attribute data in A-RAM (attribute RAM). Figure 16 shows a display example using each attribute function.

The attribute functions are offered only in character mode, and controlled either by bit 0 of the mode register (R22) or the AT pin. As shown in Figure 17, a character attribute can be specified by placing the character code on MD0–MD7, and the attribute code on MD11–MD15. MD8–MD10 are invalid.

Figure 16 Display Example Using Attribute Functions

| MD Input | 15                         | 14                         | 13       | 12     | 11               | 10–8 | 7–0            |

|----------|----------------------------|----------------------------|----------|--------|------------------|------|----------------|

| Function | Non-<br>display<br>(black) | Non-<br>display<br>(white) | Blinking | Cursor | Reverse<br>video | ***  | Character code |

### Figure 17 Attribute Code

### **OR Function** — Superimposing Characters and Graphics

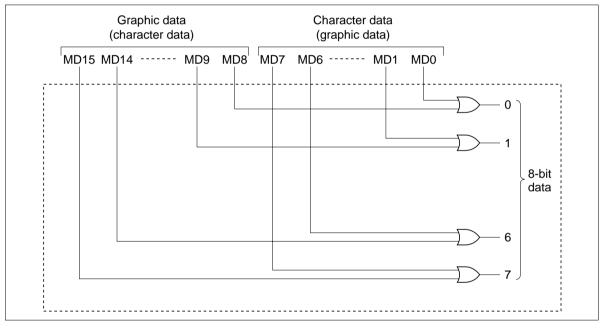

The OR function (Figure 18) generates the OR of the data entered into MD0–MD7 (e.g. character data) and the data into MD8–MD15 (e.g. graphic data) in the LCTC and transfers this data as 1 byte.

This function is offered only in character mode, and controlled by bit 0 of the mode register (R22) or by the AT pin. Any attribute functions are disabled when using the OR function.

Figure 18 OR Function

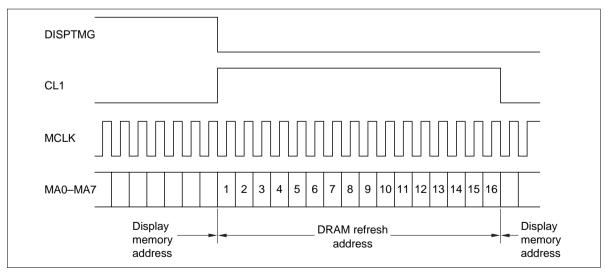

### **DRAM Refresh Address Output Function**

The LCTC outputs the address for DRAM refresh while CL1 is high, as shown in Figure 19. The 16 refresh addresses per scanned line are output 16 times, from \$00–\$FF.

#### **Skew Function**

The LCTC can specify the skew (delay) for CUDISP, DISPTMG, CL2 outputs and MD inputs.

If buffer memory and character generator ROM cannot be accessed within one horizontal character display period, the access is retarded to the next cycle by inserting a latch to memory address output and buffer memory output. The skew function retards the CUDISP, DISPTMG, CL2 outputs, and MD inputs in the LCTC to match phase with the display data signal.

By utilizing this function, a low-speed memory can be used as a buffer RAM or a character generator ROM.

This function is controlled by pins SK0 and SK1 as shown in Table 7.

#### Table 7Skew Function

| SK0 | SK1 | Skew Function         |

|-----|-----|-----------------------|

| 0   | 0   | No skew               |

| 1   | 0   | 1 character time skew |

| 0   | 1   | 2 character time skew |

| 1   | 1   | Inhibited combination |

Figure 19 DRAM Refresh Address Output

#### Easy Mode

This mode utilizes software for systems using the CRTC (HD6845). By setting MODE pin to high, the display mode and screen format are fixed as shown in Table 8. With this mode, software for a CRT screen can be utilized in a system using the LCTC, without changing the BIOS.

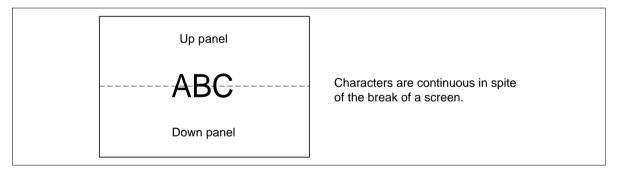

### Automatic Correction of Down Panel Raster Address

When the LCTC mode is set for character display and dual screen, memory addresses (MA) and raster addresses (RA) are output in such a way as to keep continuity of a display spread over the two panels. Therefore users can use the LCTC without considering the multiplexing duty ratio (the number of vertical dots of a screen) or the character font. (See Figure 20.)

### Table 8Fixed Values in Easy Mode

| Reg. No. | Register Name                   | Fixed Value (Decimal)       |

|----------|---------------------------------|-----------------------------|

| R9       | Maximum raster address          | 7                           |

| R10      | Cursor start raster             | 6                           |

| R11      | Cursor end raster               | 7                           |

| R18      | Horizontal virtual screen width | Same value as (R1)          |

| R19      | Multiplexing duty ratio (H)     | 99 (in dual screen mode)    |

| R20      | Multiplexing duty ratio (L)     | 199 (in single screen mode) |

| R21      | Display start raster            | 0                           |

| R22      | Mode register                   | 0                           |

Figure 20 Example of the Display in the Character Mode

### System configuration and Mode Setting

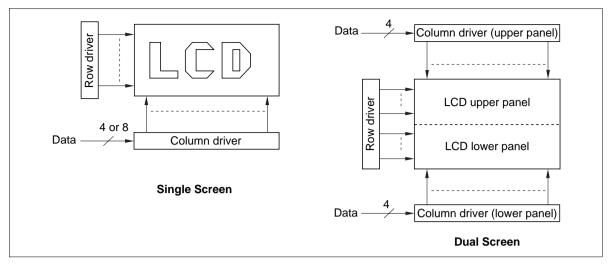

### **LCD System Configuration**

The screen configuration, single or dual, must be specified when using the LCD system (Figure 21).

Using the single screen configuration, you can construct an LCD system with lower cost than a dual screen system, since the required number of column drivers is smaller and the manufacturing process for mounting them is simpler. However, there are some limitations, such as duty ratio, breakdown voltage of a driver, and display quality of the liquid crystal, in single screen configuration. Thus, a dual screen configuration may be more suitable to an application.

The LCTC also offers an 8-bit LCD data transfer function to support an LCD screen with a smaller interval of signal input terminals. For a general size LCD screen, such as  $640 \times 200$  single, or  $640 \times 400$  dual, the usual 4-bit LCD data transfer is satisfactory.

#### Hardware Configuration and Mode Setting

The LCTC supports the following hardware configurations:

- Single or dual screen configuration

- 4-or 8-bit LCD data transfer

and the following screen format:

- Character, graphic 1, or graphic 2 display

- Normal or wide display (only in character mode)

- OR or attribute display (only in character mode)

Also, the LCTC supports up to 40 Mbits/s of large screen mode (mode 13) for large screen display. This mode is provided only in graphic 1 mode.

Table 9 shows the mode selection method according to hardware configuration and screen format. Table 10 shows how they are specified.

Figure 21 Hardware Configuration According to Screen Format

#### Table 9Mode Selection

| Hardw                | vare Configu                 | iration        |                       |                 | Screen Fo        | rmat                                     |          |

|----------------------|------------------------------|----------------|-----------------------|-----------------|------------------|------------------------------------------|----------|

| LCD Data<br>Transfer | Screen<br>Configu-<br>ration | Screen<br>Size | Character/<br>Graphic | Normal/<br>Wide | Attribute/<br>OR | Maximum<br>Data Transfer<br>Speed (Mbps) | Mode No. |

| 4-bit                | Single                       | Normal         | Character             | Normal          | AT<br>OR         | 20                                       | 5        |

|                      |                              |                |                       | Wide            | AT<br>OR         | 10                                       | 6        |

|                      |                              |                | Graphic 1             |                 |                  | 20                                       | 7        |

|                      |                              |                | Graphic 2             |                 |                  | 20                                       | 8        |

|                      | Dual                         | Normal         | Character             | Normal          | AT<br>OR         | 20                                       | 1        |

|                      |                              |                |                       | Wide            | AT<br>OR         | 10                                       | 2        |

|                      |                              |                | Graphic 1             |                 |                  | 20                                       | 3        |

|                      |                              |                | Graphic 2             |                 |                  | 20                                       | 4        |

|                      |                              | Large          | Graphic 1             |                 |                  | 40                                       | 13       |

| 8-bit                | Single                       | Normal         | Character             | Normal          | AT<br>OR         | 20                                       | 9        |

|                      |                              |                |                       | Wide            | AT<br>OR         | 10                                       | 10       |

|                      |                              |                | Graphic 1             |                 |                  | 20                                       | 11       |

|                      |                              |                | Graphic 2             |                 |                  | 20                                       | 12       |

Note: Maximum data transfer speed indicates amount of the data read out of a memory. Thus, the data transfer speed sent to the LCD driver in wide function is 20 Mbps.

### Mode List

### Table 10 Mode List

|     |                         |     |     | Pin Na | me   |    | Screen         | Graphic/  | Data        | Wide    |           |

|-----|-------------------------|-----|-----|--------|------|----|----------------|-----------|-------------|---------|-----------|

| No. | Mode Name               | D/S | G/C | LS     | WIDE | AT | Config.        | Character | Transfer    | Display | Attribute |

| 1   | Dual-screen character   | 1   | 0   | 0      | 0    | 0  | Dual           | Character | 4-bit       | Normal  | OR        |

|     |                         | 1   | 0   | 0      | 0    | 1  | screen         |           | ×2          |         | AT        |

| 2   | Dual-screen wide        | 1   | 0   | 0      | 1    | 0  |                |           |             | Wide    | OR        |

|     | character               | 1   | 0   | 0      | 1    | 1  |                |           |             |         | AT        |

| 3   | Dual-screen graphic 1   | 1   | 1   | 0      | 0    | 1  | _              | Graphic   | -           | _       |           |

| 4   | Dual-screen graphic 2   | 1   | 1   | 0      | 0    | 0  |                |           |             |         |           |

| 5   | Single-screen character | 0   | 0   | 0      | 0    | 0  | Single         | Character | 4-bit       | Normal  | OR        |

|     |                         | 0   | 0   | 0      | 0    | 1  | screen         |           |             |         | AT        |

| 6   | Single-screen wide      | 0   | 0   | 0      | 1    | 0  |                |           |             | Wide    | OR        |

|     | character               | 0   | 0   | 0      | 1    | 1  |                |           |             |         | AT        |

| 7   | Single-screen graphic 1 | 0   | 1   | 0      | 0    | 1  |                | Graphic   | -           | _       | _         |

| 8   | Single-screen graphic 2 | 0   | 1   | 0      | 0    | 0  |                |           |             |         |           |

| 9   | 8-bit character         | 0   | 0   | 1      | 0    | 0  | Single         | Character | 8-bit       | Normal  | OR        |

|     |                         | 0   | 0   | 1      | 0    | 1  | screen         |           |             |         | AT        |

| 10  | 8-bit wide character    | 0   | 0   | 1      | 1    | 0  |                |           |             | Wide    | OR        |

|     |                         | 0   | 0   | 1      | 1    | 1  |                |           |             |         | AT        |

| 11  | 8-bit graphic 1         | 0   | 1   | 1      | 0    | 1  | _              | Graphic   | -           | _       | _         |

| 12  | 8-bit graphic 2         | 0   | 1   | 1      | 0    | 0  | _              |           |             |         |           |

| 13  | Large screen            | 1   | 1   | 1      | 0    | 1  | Dual<br>screen | _         | 4-bit<br>×2 | -       |           |

The LCTC display mode is determined by pins  $D/\overline{S}$  (pin 55),  $G/\overline{C}$  (pin 58), LS (pin 56), WIDE (pin 54), and AT (pin 57). As for G/C, WIDE, and AT, the OR is taken between data bits 0, 2, and 3 of the mode register (R22). The display mode can be controlled by either one of the external pins or the data bits of R22.

Note: The above 5 pins have 32 status combinations (high and low). Any combinations other than the above are prohibited, because they may cause malfunctions. If you set an prohibited combination, set the right combination again.

### **Internal Registers**

The HD64645/HD64646 has one address register and fourteen data registers. In order to select one out of fourteen data registers, the address of the data register to be selected must be written into the address register. The MPU can transfer data to/from the data register corresponding to the written address.

To be software compatible with the CRTC (HD6845), registers R2–R8, R16, and R17, which are not necessary for an LCD are defined as invalid for the LCTC.

#### Address Register (AR)

AR register (Figure 22) specifies one out of 14 data registers. Address data is written into the address register when RS is low. If no register corresponding to a specified address exists, the address data is invalid.

#### Horizontal Total Characters Register (R0)

R0 register (Figure 23) specifies a horizontal scanning period. The total number of horizontal characters less 1 must be programmed into this 8-bit register in character units. Nht indicates the horizontal scanning period including the period when the CPU occupies memory (total number of horizontal characters minus the number of horizontal displayed characters). Its units are, then, converted from time into the number of characters. This value should be specified according to the specification of the LCD system to be used.

Note the following restrictions

Nhd +

$$\frac{16}{m} \leq Nht + 1$$

| Mode No.                   | m |  |

|----------------------------|---|--|

| 5,9                        | 1 |  |

| 1, 6, 7, 8, 10, 11, 12, 13 | 2 |  |

| 2, 3, 4                    | 4 |  |

### Horizontal Displayed Characters Register (R1)

R1 register (Figure 24) specifies the number of characters displayed per row. The horizontal character pitches are 8 bits for normal character display and 16 dots for wide character display and graphic display.

Nhd must be less than the total number of horizontal characters.

### Maximum Raster Address Register (R9)

R9 register (Figure 25) specifies the number of rasters per row in characters mode, consisting of 5 bits. The programmable range is 0 (1 raster/row) to 31 (32 rasters/row).

|   |   |   | Data | a Bit | t    |      |     | Program Unit | R/W |

|---|---|---|------|-------|------|------|-----|--------------|-----|

| 7 | 6 | 5 | 4    | 3     | 2    | 1    | 0   |              |     |

| _ | — | - | Re   | egist | er a | ddre | ess |              | W   |

#### Figure 22 Address Register

|   |     |       | Data  | a Bit |      |       |   | Program Unit | R/W |

|---|-----|-------|-------|-------|------|-------|---|--------------|-----|

| 7 | 6   | 5     | 4     | 3     | 2    | 1     | 0 |              |     |

|   | Nht | (tota | al ch | arac  | ters | s – 1 | ) | Character    | W   |

#### Figure 23 Horizontal Total Characters Register

|   |       |      | Data  | a Bit |      |      |    | Program Unit | R/W |

|---|-------|------|-------|-------|------|------|----|--------------|-----|

| 7 | 6     | 5    | 4     | 3     | 2    | 1    | 0  |              |     |

| N | lhd ( | disp | olaye | ed cl | hara | cter | s) | Character    | W   |

#### Figure 24 Horizontal Displayed Characters Register

|   |   |   | Data | a Bit |    |   |   | Program Unit | R/W |

|---|---|---|------|-------|----|---|---|--------------|-----|

| 7 | 6 | 5 | 4    | 3     | 2  | 1 | 0 |              |     |

| — | — | — |      |       | Nr |   |   | Raster       | W   |

### Figure 25 Maximum Raster Address Register

#### Cursor Start Raster Register (R10)

R10 register (Figure 26) specifies the cursor start raster address and its blink mode. Refer to Table 11.

32- or 64-frame

### Cursor End Raster Register (R11)

R11 register (Figure 27) specifies the cursor end raster address.

### Start Address Register (H/L) (R12/R13)

R12/R13 register (Figure 28) specifies a buffer memory read start address. Updating this register facilitates paging and scrolling. R14/R15 register can be read and written to/from the MPU.

#### Cursor Address Register (H/L) (R14/R15)

R14/R15 register (Figure 29) specifies a cursor display address. Cursor display requires setting R10 and R11, and CUDISP should be connected with MD12 (in character mode). This register can be read from and written to the MPU.

#### Horizontal Virtual Screen Width Register (R18)

R18 register (Figure 30) specifies the memory width to determine the start address of the next row. By using this register, memory width can be specified larger than the number of horizontal displayed characters. Updating the display start address facilitates scrolling in any direction within a memory space.

The start address of the next row is that of the previous row plus Nir. If a larger memory width than display width is unnecessary, Nir should be set equal to the number of horizontal displayed characters.

#### Table 11 Cursor Blink Mode

| В | Р | Cursor Blink Mode             |

|---|---|-------------------------------|

| 0 | 0 | Cursor on; without blinking   |

| 0 | 1 | Cursor off                    |

| 1 | 0 | Blinking once every 32 frames |

| 1 | 1 | Blinking once every 64 frames |

|   |   |   | Data | a Bit  | :      |      |      | Program Unit | R/W |

|---|---|---|------|--------|--------|------|------|--------------|-----|

| 7 | 6 | 5 | 4    | 3      | 2      | 1    | 0    |              |     |

| — | В | Р | Ncs  | s (ras | ster a | addr | ess) | Raster       | W   |

Figure 26 Cursor Start Raster Register

|   |   |   |   | Data | a Bit  | :      |       |      | Program Unit | R/W |

|---|---|---|---|------|--------|--------|-------|------|--------------|-----|

| - | 7 | 6 | 5 | 4    | 3      | 2      | 1     | 0    |              |     |

| - | - | _ | - | Nce  | e (ras | ster a | addre | ess) | Raster       | W   |

### Figure 27 Cursor End Raster Register

| 7         6         5         4         3         2         1         0           Memory address (H) (R12)         Memory R/W |   |   |   | Data | a Bit |          |         | Program Unit | R/W |

|-------------------------------------------------------------------------------------------------------------------------------|---|---|---|------|-------|----------|---------|--------------|-----|

|                                                                                                                               | 7 | - | - | •    |       | 1<br>(R1 | 0<br>2) | Memory       | R/W |

Figure 28 Start Address Register

|   |      |                                                                                                                                         | I   | Data | a Bit |     |   |    | Program Unit | R/W  |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|-----|---|----|--------------|------|

| 7 |      |                                                                                                                                         | -   | 4    | 3     | 2   | 1 | 0  | -            | 5.44 |

|   |      | Data Bit     Program Unit     R/W       6     5     4     3     2     1     0       lemory address (L) (R15)     Memory address     R/W |     |      |       |     |   |    |              |      |

|   | IVIE |                                                                                                                                         | лус | JUUI | 632   | (Ľ) |   | 5) |              |      |

#### Figure 29 Cursor Address Register

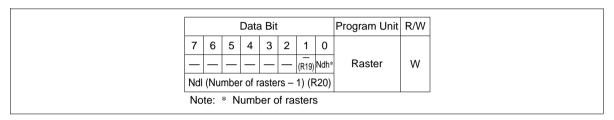

### Multiplexing Duty Ratio Register (H/L) (R19/R20)

R19/R20 register (Figure 31) specifies the number of vertical dots of the display screen. The programmed value differs according to the LCD screen configuration.

In single screen configuration:

(Programmed value) = (Number of vertical dots) -1

In dual screen configuration:

(Programmed value) =  $\frac{(\text{Number of vertical dots})}{2}$  -1

### **Display Start Raster Register (R21)**

R21 register (Figure 32) specifies the start raster of the character row displayed on the top of the screen. The programmed value should be equal or less than the maximum raster address. Updating this register allows smooth scrolling in character mode.

### Mode Register (R22)

The Or of the data bits of R22 (Figure 33) register and the external terminals of the same name determines a particular mode (Figure 34).

| I              | Data E  | Bit  |        |        |      | Program Unit | R/W |

|----------------|---------|------|--------|--------|------|--------------|-----|

| 7 6 5          | 4 3     | 3    | 2      | 1      | 0    |              |     |

| Nir (No. of cl | hars. c | of v | rirtua | ıl wio | dth) | Character    | W   |

### Figure 30 Horizontal Virtual Screen Width Register

### Figure 31 Multiplexing Duty Ratio Register

|   |   |   |   | Data | a Bit |       |      |    | Program Unit | R/W |

|---|---|---|---|------|-------|-------|------|----|--------------|-----|

| 7 | 7 | 6 | 5 | 4    | 3     | 2     | 1    | 0  |              |     |

| _ |   | _ | — | R    | aste  | er ac | Idre | SS | Raster       | W   |

### Figure 32 Display Start Raster Register

|   |   |   | Data I | Bit |      |     |    | Program Unit | R/W |

|---|---|---|--------|-----|------|-----|----|--------------|-----|

| 7 | 6 | 5 | 4      | 3   | 2    | 1   | 0  |              |     |

| _ | - | - | ON/OFF | G/C | WIDE | BLE | AT | _            | W   |

### Figure 33 Mode Register

Figure 34 Correspondence between Mode Register and External Pins

#### **Restrictions on Programming Internal Registers**

Note when programming that the values you can write into the internal registers are restricted as shown in Table 12.

| Function           | Restrictions                                                                                                                                                                                                             | Register     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Display format     | 1 < Nhd < Nht + 1 ≤ 256                                                                                                                                                                                                  | R0, R1       |

|                    | Nhd + $\frac{16}{m} \times 1 \le Nht + 1$                                                                                                                                                                                |              |

|                    | (No. of vertical dots) × (No. of horizontal dots) ×<br>(frame frequency; fFRM) ≤ (data transfer speed; V)<br>$\begin{cases} 1\\2 \end{cases}^{*2} × (Nd + 1) × Nhd × \begin{cases} 8\\16 \end{cases}^{*3} f_{FRM} \le V$ | R1, R19, R20 |

|                    | Nhd ≤ Nir                                                                                                                                                                                                                | R1, R18      |

|                    | $0 \leq Ndi \leq 511$                                                                                                                                                                                                    | R19, R20     |

| Cursor control     | $0 \le Ncs \le Nce$                                                                                                                                                                                                      | R10, R11     |

|                    | Nce ≤ Nr                                                                                                                                                                                                                 | R10, R9      |

| Smooth scroll      | Nsr ≤ Nr                                                                                                                                                                                                                 | R21, R9      |

| Memory width set   | $0 \le Nir \le 255$                                                                                                                                                                                                      | R18          |

| Notes: 1. m varies | according to the modes. See the following table.                                                                                                                                                                         |              |

| Mode No            | o. m                                                                                                                                                                                                                     |              |

| F 0                | 1                                                                                                                                                                                                                        |              |

#### Table 12 Restrictions on Writing Values into the Internal Registers

| Mode No.                   | m |  |

|----------------------------|---|--|

| 5, 9                       | 1 |  |

| 1, 6, 7, 8, 10, 11, 12, 13 | 2 |  |

| 2, 3, 4                    | 4 |  |

|                            |   |  |

2. Set 1 when an LCD screen is a single screen, and set 2 when dual. Modes are classified as shown in the following table.

| Mode No.                  | Value |

|---------------------------|-------|

| 5, 6, 7, 8, 9, 10, 11, 12 | 1     |

| 1, 2, 3, 4, 13            | 2     |

3. Set 8 when a character is constructed with 8 dots, and set 16 when with 16 dots. Modes are classified as shown in the following table.

| Mode No.                         | Value |  |  |

|----------------------------------|-------|--|--|

| 1, 5, 9                          | 8     |  |  |

| 2, 3, 4, 6, 7, 8, 10, 11, 12, 13 | 16    |  |  |

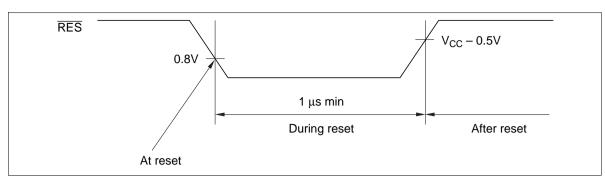

#### Reset

$\overline{\text{RES}}$  pin determines the internal state of LSI counters and the like. This pin does not affect register contents nor does it basically control output terminals.

Reset is defined as follows (Figure 35):

- At reset: the time when  $\overline{\text{RES}}$  goes low

- During reset: the period while RES remains low

- After reset: the period on and after the  $\overline{\text{RES}}$  transition from low to high

- Make sure to hold the reset signal low for at least 1 µs

$\overline{\text{RES}}$  pin should be pulled high by users during operation.

#### **Reset State of Pins**

RES pin does not basically control output pins, and operates regardless of other input pins.

- 1. Preserve states before reset LU0–LU3, LD0–LD3, FLM, CL1, RA0–RA4

- Fixed at high level MLCK

- Preserve states before reset or fixed at low level according to the timing when the reset signal is input DISPTMG, CUDISP, MA0–MA15

- 4. Fixed at high or low according to mode CL2

- 5. Unaffected DB0–DB7

#### **Reset State of Registers**

$\overline{\text{RES}}$  pin does not affect register contents. Therefore, registers can be read or written even during a reset state; their contents will be preserved regardless of reset until they are rewritten to.

#### Notes for HD64645/HD64646

- 1. The HD64645/HD64646 are CMOS LSIs, and it should be noted that input pins must not be left disconnected, etc.

- 2. At power-on, the state of internal registers becomes undefined. The LSI operation is undefined until all internal registers have been programmed.

Figure 35 Reset Definition

## **Absolute Maximum Ratings**

| Item                  | Symbol           | Value              | Note |  |

|-----------------------|------------------|--------------------|------|--|

| Supply voltage        | V <sub>cc</sub>  | –0.3 to +7.0V      | 2    |  |

| Terminal voltage      | Vin              | -0.3 to VCC + 0.3V | 2    |  |

| Operating temperature | T <sub>opr</sub> | –20°C to +75°C     |      |  |

| Storage temperature   | T <sub>stg</sub> | –55°C to +125°C    |      |  |

Notes: 1. Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions ( $V_{cc} = 5.0V \pm 10\%$ , GND = 0V, Ta = -20°C to +75°C). If these conditions are exceeded, it could affect reliability of LSI.

2. With respect to ground (GND = 0V)

## **Electrical Characteristics**

| ltem                                          |                              | Symbol           | Min            | Тур | Max                   | Unit | Test Condition            |

|-----------------------------------------------|------------------------------|------------------|----------------|-----|-----------------------|------|---------------------------|

| Input high<br>voltage                         | RES, MODE,<br>SK0, SK1       | VIH              | $V_{cc} - 0.5$ |     | V <sub>cc</sub> + 0.3 | V    |                           |

|                                               | DCLK, ON/OFF                 | _                | 2.2            |     | V <sub>cc</sub> + 0.3 | V    |                           |

|                                               | All others                   |                  | 2.0            |     | V <sub>cc</sub> + 0.3 | V    |                           |

| Input low<br>voltage                          | All others                   | VIL              | -0.3           |     | 0.8                   | V    |                           |

| Output high                                   | TTL interface*1              | VOH              | 2.4            |     |                       | V    | I <sub>OH</sub> = -400 μA |

| voltage                                       | CMOS interface*1             | _                | $V_{cc} - 0.8$ |     |                       | V    | I <sub>OH</sub> = -400 μA |

| Output low                                    | TTL interface                | VOL              |                |     | 0.4                   | V    | I <sub>oL</sub> = 1.6 mA  |

| voltage                                       | CMOS interface               |                  |                |     | 0.8                   | V    | I <sub>oL</sub> = 400 μA  |

| Input leakage current                         | All inputs except<br>DB0–DB7 | I <sub>IL</sub>  | -2.5           |     | +2.5                  | μΑ   |                           |

| Three state<br>(off-state)<br>leakage current | DB0-DB7                      | I <sub>TSL</sub> | -10            |     | +10                   | μΑ   |                           |

| Current dissipation*2                         |                              | I <sub>cc</sub>  |                |     | 10                    | mA   |                           |

DC Characteristics ( $V_{CC} = 5.0V \pm 10\%$ , GND = 0V,  $T_a = -20^{\circ}C$  to +75°C, unless otherwise noted)

Notes: 1. TTL Interface; MA0–MA15, RA0–RA4, DISPTMG, CUDISP, DB0–DB7, MCLK C-MOS Interface; LU0–LU3, LD0–LD3, CL1, CL2, M, FLM

2. Input/output current is excluded. When input is at the intermediate level with CMOS, excessive current flows through the input circuit to power supply. Input level must be fixed at high or low to avoid this condition.

3. If the capacitive loads of LU0–LU3 and LD0–LD3 exceed the rating, noise over 0.8 V may be produced on CUDISP, DISPTMG, MCLK, FLM and M. In case the loads of LU0–LU3 and LD0–LD3 are larger than the ratings, supply signals to the LCD module through buffers.

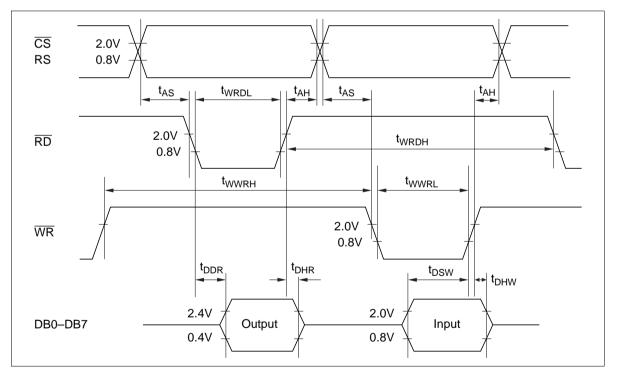

#### **AC Characteristics**

| Item                      | Symbol            | Min | Тур | Мах | Unit | Figure |

|---------------------------|-------------------|-----|-----|-----|------|--------|

| RD high level width       | t <sub>wrdh</sub> | 190 |     |     | ns   | 36     |

| RD low level width        | t <sub>wrdl</sub> | 190 |     |     | ns   |        |

| WR high level width       | t <sub>wwRH</sub> | 190 |     |     | ns   |        |

| WR low level width        | t <sub>wwRL</sub> | 190 |     |     | ns   |        |

| CS, RS setup time         | t <sub>AS</sub>   | 0   |     |     | ns   |        |

| CS, RS hold time          | t <sub>AH</sub>   | 0   |     |     | ns   |        |

| DB0–DB7 setup time        | t <sub>DSW</sub>  | 100 |     |     | ns   |        |

| DB0–DB7 hold time         | t <sub>DHW</sub>  | 0   |     |     | ns   |        |

| DB0–DB7 output delay time | t <sub>DDR</sub>  |     |     | 150 | ns   |        |

| DB0–DB7 output hold time  | t <sub>DHR</sub>  | 20  |     |     | ns   |        |

Figure 36 CPU Interface

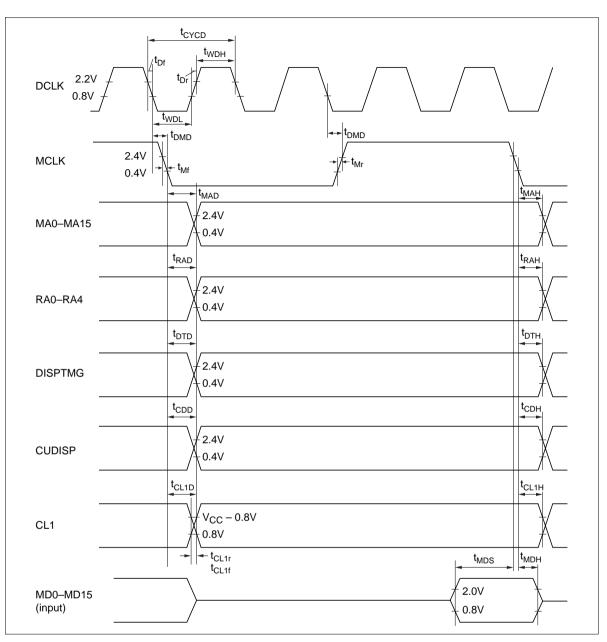

| Item                  | Symbol            | Min | Тур | Max | Unit | Figure |

|-----------------------|-------------------|-----|-----|-----|------|--------|

| DCLK cycle time       | t <sub>CYCD</sub> | 100 |     | _   | ns   | 37     |

| DCLK high level width | t <sub>wDH</sub>  | 30  | _   | _   | ns   |        |

| DCLK low level width  | t <sub>WDL</sub>  | 30  | _   | _   | ns   |        |

| DCLK rise time        | t <sub>Dr</sub>   | —   |     | 20  | ns   |        |

| DCLK fall time        | t <sub>Df</sub>   | —   |     | 20  | ns   |        |

| MCLK delay time       | t <sub>DMD</sub>  | —   | —   | 60  | ns   |        |

| MCLK rise time        | t <sub>Mr</sub>   | —   | _   | 30  | ns   |        |

| MCLK fall time        | t <sub>Mf</sub>   | —   | _   | 30  | ns   |        |

| MA0-MA15 delay time   | t <sub>MAD</sub>  | _   | _   | 150 | ns   |        |

| MA0–MA15 hold time    | t <sub>MAH</sub>  | 10  | _   | _   | ns   |        |

| RA0–RA4 delay time    | t <sub>RAD</sub>  | _   | _   | 150 | ns   |        |

| RA0–RA4 hold time     | t <sub>RAH</sub>  | 10  | _   | _   | ns   |        |

| DISPTMG delay time    | t <sub>DTD</sub>  | —   | _   | 150 | ns   |        |

| DISPTMG hold time     | t <sub>DTH</sub>  | 10  | _   | _   | ns   |        |

| CUDISP delay time     | t <sub>CDD</sub>  | _   | _   | 150 | ns   |        |

| CUDISP hold time      | t <sub>CDH</sub>  | 10  | _   | _   | ns   |        |

| CL1 delay time        | t <sub>CL1D</sub> | _   | _   | 150 | ns   |        |

| CL1 hold time         | t <sub>cl1H</sub> | 10  | _   |     | ns   |        |

| CL1 rise time         | t <sub>CL1r</sub> | _   | _   | 50  | ns   |        |

| CL1 fall time         | t <sub>CL1f</sub> | _   | _   | 50  | ns   |        |

| MD0–MD15 setup time   | t <sub>MDS</sub>  | 30  | _   | _   | ns   |        |

| MD0–MD15 hold time    | t <sub>MDH</sub>  | 15  | _   |     | ns   |        |

Figure 37 Memory Interface

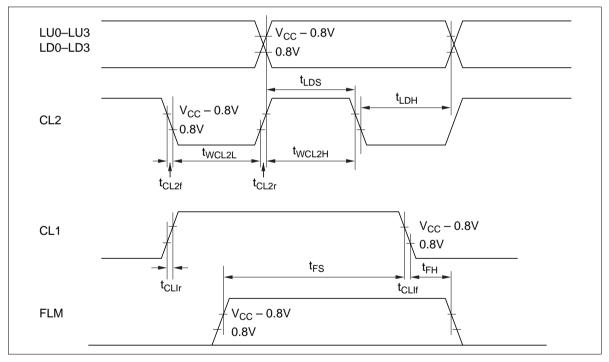

#### LCD Interface 1 (HD64645) ( $V_{CC} = 5.0V \pm 10\%$ , GND = 0V, $T_a = -20^{\circ}C$ to $+75^{\circ}C$ )

| Item                    | Symbol             | Min | Тур | Max | Unit | Figure |

|-------------------------|--------------------|-----|-----|-----|------|--------|

| Display data setup time | t <sub>LDS</sub>   | 50  | —   | —   | ns   | 38     |

| Display data hold time  | t <sub>LDH</sub>   | 100 | _   | _   | ns   |        |

| CL2 high level width    | t <sub>WCL2H</sub> | 100 | _   | _   | ns   |        |

| CL2 low level width     | t <sub>WCL2L</sub> | 100 | _   | _   | ns   |        |

| FLM setup time          | t <sub>FS</sub>    | 500 | _   | _   | ns   |        |

| FLM hold time           | t <sub>FH</sub>    | 300 | _   | _   | ns   |        |

| CL1 rise time           | t <sub>CL1r</sub>  |     | —   | 50  | ns   |        |

| CL1 fall time           | t <sub>CL1f</sub>  |     | _   | 50  | ns   |        |

| CL2 rise time           | t <sub>CL2r</sub>  |     | _   | 50  | ns   |        |

| CL2 fall time           | t <sub>CL2f</sub>  |     | —   | 50  | ns   |        |

Note: At  $f_{CL2} = 3 \text{ MHz}$

Figure 38 LCD Interface

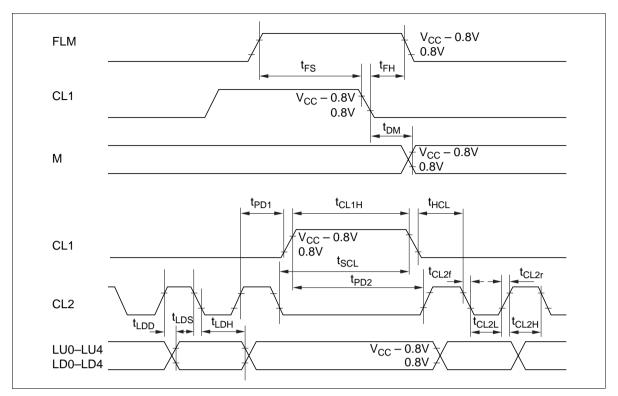

| Item                    | Symbol            | Min | Тур | Мах | Unit | Figure |

|-------------------------|-------------------|-----|-----|-----|------|--------|

| FLM setup time          | t <sub>Fs</sub>   | 500 | —   |     | ns   | 39     |

| FLM hold time           | t <sub>FH</sub>   | 300 | _   |     | ns   |        |

| M delay time            | t <sub>DM</sub>   |     | _   | 200 | ns   |        |

| CL1 high level width    | t <sub>cL1H</sub> | 300 | _   |     | ns   |        |

| Clock setup time        | t <sub>scl</sub>  | 500 | _   |     | ns   |        |

| Clock hold time         | t <sub>HCL</sub>  | 100 | _   |     | ns   |        |

| Phase difference 1      | t <sub>PD1</sub>  | 100 | _   |     | ns   |        |

| Phase difference 2      | t <sub>PD2</sub>  | 500 | _   |     | ns   |        |

| CL2 high level width    | t <sub>CL2H</sub> | 100 | _   |     | ns   |        |

| CL2 low level width     | t <sub>CL2L</sub> | 100 | _   |     | ns   |        |

| CL2 rise time           | t <sub>CL2r</sub> |     | _   | 50  | ns   |        |

| CL2 fall time           | t <sub>CL2f</sub> | —   | —   | 50  | ns   |        |

| Display data setup time | t <sub>LDS</sub>  | 80  | _   |     | ns   |        |

| Display data hold time  | t <sub>LDH</sub>  | 100 | _   |     | ns   |        |

| Display data delay time | t <sub>LDD</sub>  |     | _   | 30  | ns   |        |

LCD Interface 2 (HD64646 at  $f_{CL2} = 3$  MHz) ( $V_{CC} = 5.0V \pm 10\%$ , GND = 0V,  $T_a = -20^{\circ}C$  to  $+75^{\circ}C$ )

## LCD Interface 3 (HD64646 at $f_{CL2}$ = 5 MHz) (V<sub>CC</sub> = 5.0V ± 10%, GND = 0V, T<sub>a</sub> = -20°C to +75°C)

| Item                    | Symbol            | Min | Тур | Max | Unit | Figure |

|-------------------------|-------------------|-----|-----|-----|------|--------|

| FLM setup time          | t <sub>Fs</sub>   | 500 |     |     | ns   | 39     |

| FLM hold time           | t <sub>FH</sub>   | 200 |     |     | ns   |        |

| M delay time            | t <sub>DM</sub>   | _   |     | 200 | ns   |        |

| CL1 high level width    | t <sub>cL1H</sub> | 300 |     |     | ns   |        |

| Clock setup time        | t <sub>scl</sub>  | 500 |     |     | ns   |        |

| Clock hold time         | t <sub>HCL</sub>  | 100 |     | _   | ns   |        |

| Phase difference 1      | t <sub>PD1</sub>  | 70  |     |     | ns   |        |

| Phase difference 2      | t <sub>PD2</sub>  | 500 |     |     | ns   |        |

| CL2 high level width    | t <sub>CL2H</sub> | 50  |     |     | ns   |        |

| CL2 low level width     | t <sub>CL2L</sub> | 50  |     |     | ns   |        |

| CL2 rise time           | t <sub>CL2r</sub> | —   | _   | 50  | ns   |        |

| CL2 fall time           | t <sub>CL2f</sub> | —   | _   | 50  | ns   |        |

| Display data setup time | $t_{LDS}$         | 30  | _   |     | ns   |        |

| Display data hold time  | t <sub>LDH</sub>  | 30  | _   |     | ns   |        |

| Display data delay time | $t_{LDD}$         | —   |     | 30  | ns   |        |

Figure 39 LCD Interface

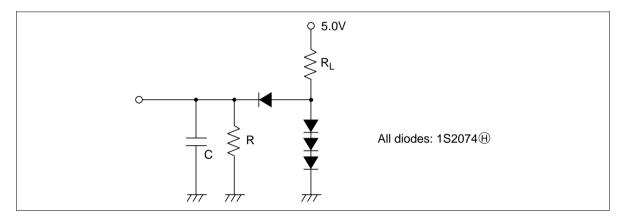

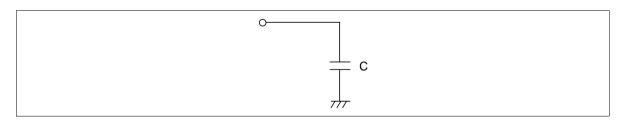

## Load Circuit

TTL Load

| Terminal                           | $R_L$  | R     | С      | Remarks               |

|------------------------------------|--------|-------|--------|-----------------------|

| DB0–DB7                            | 2.4 kΩ | 11 kΩ | 130 pF | tr, tf: Not specified |

| MA0-MA15, RA0-RA4, DISPTMG, CUDISP | 2.4 kΩ | 11 kΩ | 40 pF  | _                     |

| MCLK                               | 2.4 kΩ | 11 kΩ | 30 pF  | tr, tf: Specified     |

#### **Capacitive Load**

| Terminal            | C      | Remarks               |

|---------------------|--------|-----------------------|

| CL2                 | 150 pF | tr, tf: Specified     |

| CL1                 | 200 pF |                       |

| LU0–LU3, LD0–LD3, M | 150 pF | tr, tf: Not specified |

| FLM                 | 50 pF  |                       |

Refer to user's manual (No. 68-1-160) and application note (No. ADE-502-003) for detail of this product.

#### Cautions

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

Tel: <44> (1628) 585000 Fax: <44> (1628) 778322

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

#

| Semiconductor & Integrate<br>Nippon Bldg., 2-6-2, Ohte-<br>Tel: Tokyo (03) 3270-2111<br>URL NorthAmeric<br>Europe<br>Asia (Singap<br>Asia (Taiwar<br>Asia (HongK      | machi, Chiyoda-ku, Tokyo 100-0004,<br>Fax: (03) 3270-5109<br>a : http:semiconductor.hita<br>: http://www.hitachi-eu.c<br>ore) : http://www.has.hitachi.<br>) : http://www.hitachi.com                                                                                                                                                                                     | achi.com/                                                                                                                                                                                                                                                                                          | n                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|