# EM78F 648/644/642/641N 548/544/542/541N

# Flash Series 8-Bit Microcontroller

# Product Specification

Doc. Version 1.2

**ELAN MICROELECTRONICS CORP.**

March 2013

## **Trademark Acknowledgments:**

IBM is a registered trademark and PS/2 is a trademark of IBM. Windows is a trademark of Microsoft Corporation.

ELAN and ELAN logo are trademarks of ELAN Microelectronics Corporation.

# Copyright © 2010~2013 by ELAN Microelectronics Corporation All Rights Reserved

Printed in Taiwan

The contents of this specification are subject to change without further notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible for any claims attributed to errors, omissions, or other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall not be liable for direct, indirect, special incidental, or consequential damages arising from the use of such information or material.

The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of ELAN Microelectronics product in such applications is not supported and is prohibited.

NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS WITHOUT THE EXPRESSED WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

## **ELAN MICROELECTRONICS CORPORATION**

## Headquarters:

No. 12, Innovation 1<sup>st</sup> Road Hsinchu Science Park Hsinchu, TAIWAN 30076 Tel: +886 3 563-9977 Fax: +886 3 563-9966 webmaster@emc.com.tw

http://www.emc.com.tw

#### Korea:

## Elan Korea Electronics Company, Ltd.

301 Dong-A Building 632 Kojan-Dong, Namdong-ku Incheon City, KOREA Tel: +82 32 814-7730 Fax: +82 32 813-7730

## Hong Kong:

## Elan (HK) Microelectronics Corporation, Ltd.

Flat A, 19F., World Tech Centre 95 How Ming Street, Kwun Tong Kowloon, HONG KONG

Tel: +852 2723-3376 Fax: +852 2723-7780

#### Shenzhen:

## Elan Microelectronics Shenzhen, Ltd.

8A Floor, Microprofit Building Gaoxin South Road 6 Shenzhen Hi-tech Industrial Park South Area, Shenzhen CHINA 518057 Tel: +86 755 2601-0565

Fax: +86 755 2601-0500 elan-sz@elanic.com.cn

## USA:

## Elan Information Technology Group (U.S.A.)

PO Box 601 Cupertino, CA 95015 U.S.A.

Tel: +1 408 366-8225 Fax: +1 408 366-8225

#### Shanghai:

## Elan Microelectronics Shanghai, Ltd.

6F, Ke Yuan Building No. 5, Bibo Road Zhangjiang Hi-Tech Park Shanghai, CHINA 201203 Tel: +86 21 5080-3866 Fax: +86 21 5080-0273 elan-sh@elanic.com.cn

| 1                                                                                          | Gen   | eral Des | scription                                                        | 1  |

|--------------------------------------------------------------------------------------------|-------|----------|------------------------------------------------------------------|----|

| <ul><li>2 Features</li><li>2.1 Features Selection Guide</li><li>3 Pin Assignment</li></ul> |       |          |                                                                  |    |

|                                                                                            | 2.1   | Featur   | es Selection Guide                                               | 2  |

| 3                                                                                          | Pin . | Assignr  | nent                                                             | 3  |

|                                                                                            | 3.1   | _        | F648N / 548N Pin Assignment                                      |    |

|                                                                                            | 3.2   |          | F644N / 544N Pin Assignment                                      |    |

|                                                                                            | 3.3   |          | F642N / 542N Pin Assignment                                      |    |

|                                                                                            | 3.4   |          | F641N / 541N Pin Assignment                                      |    |

| 4                                                                                          | _     |          | tion                                                             |    |

| 7                                                                                          |       | -        |                                                                  |    |

|                                                                                            | 4.1   |          | F648N / 548N Pin Description                                     |    |

|                                                                                            | 4.2   |          | F644N / 544N Pin Description                                     |    |

|                                                                                            | 4.3   |          | F642N / 542N Pin Description                                     |    |

|                                                                                            | 4.4   |          | F641N / 541N Pin Description                                     |    |

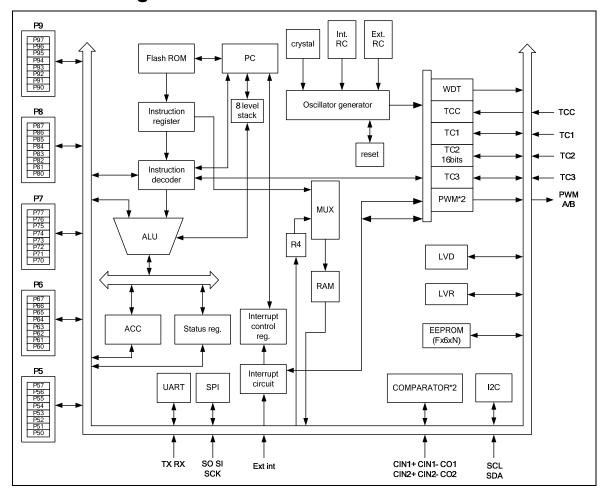

| 5                                                                                          | Bloc  | ck Diagr | ram                                                              | 12 |

| 6                                                                                          | Fun   | ctional  | Description                                                      | 13 |

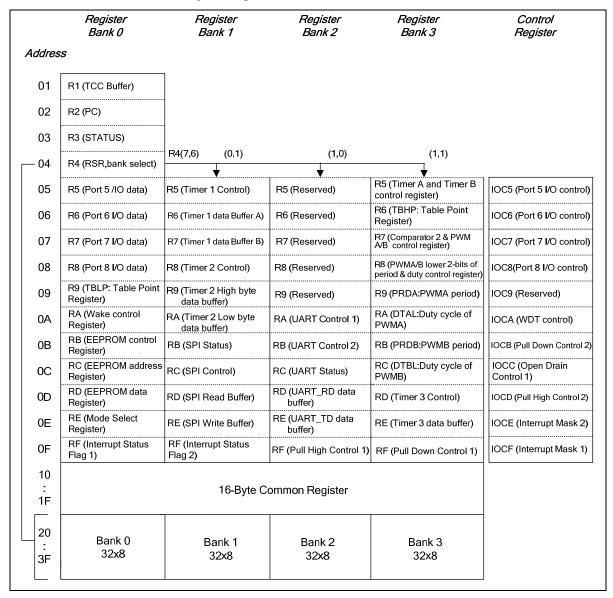

|                                                                                            | 6.1   | Operat   | tional Registers (for EM78F644/642/641/544/542/541N Series only) | 13 |

|                                                                                            |       | 6.1.1    | R0 (Indirect Addressing Register)                                | 13 |

|                                                                                            |       | 6.1.2    | R1 (Timer Clock/Counter)                                         | 13 |

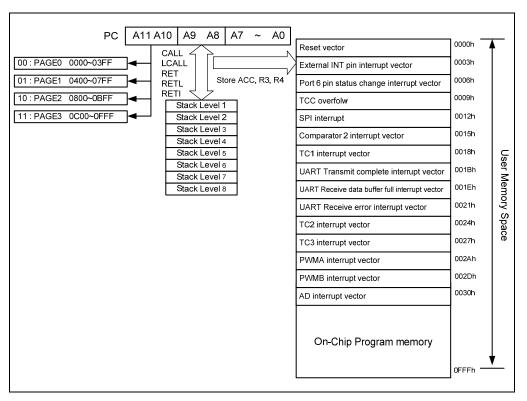

|                                                                                            |       | 6.1.3    | R2 (Program Counter and Stack)                                   | 13 |

|                                                                                            |       | 6.1.4    | R3 (Status Register)                                             | 16 |

|                                                                                            |       | 6.1.5    | R4 (RAM Select Register)                                         | 16 |

|                                                                                            |       | 6.1.6    | Bank 0 R5 (Port 5)                                               | 16 |

|                                                                                            |       | 6.1.7    | Bank 0 R6 (Port 6)                                               |    |

|                                                                                            |       | 6.1.8    | Bank 0 R7 (Port 7)                                               | 17 |

|                                                                                            |       | 6.1.9    | Bank 0 R8 (Port 8)                                               |    |

|                                                                                            |       |          | Bank 0 R9 (TBLP: Table Point Register for Instruction TBRD)      |    |

|                                                                                            |       |          | Bank 0 RA (Wake-up Control Register)                             |    |

|                                                                                            |       |          | Bank 0 RB (EEPROM Control Register)                              |    |

|                                                                                            |       |          | Bank 0 RC (256 Bytes EEPROM Address)                             |    |

|                                                                                            |       |          | Bank 0 RD (256 Bytes EEPROM Data)                                |    |

|                                                                                            |       |          | Bank 0 RE (Mode Select Register)                                 |    |

|                                                                                            |       |          | Bank 0 RF (Interrupt Status Register 1)                          |    |

|                                                                                            |       |          | R10 ~ R3F                                                        |    |

|                                                                                            |       |          | Bank 1 R5 TC1CR (Timer 1 Control)                                |    |

|                                                                                            |       |          | Bank 1 R6 TCR1DA (Timer 1 Data Buffer A)                         |    |

|                                                                                            |       | ნ.1.∠0   | Bank 1 R7 TCR1DB (Timer 1 Data Buffer B)                         | 24 |

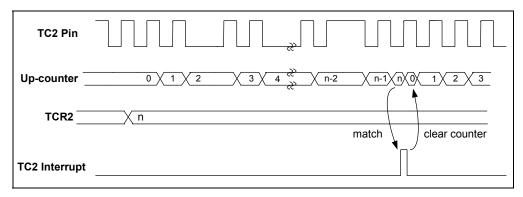

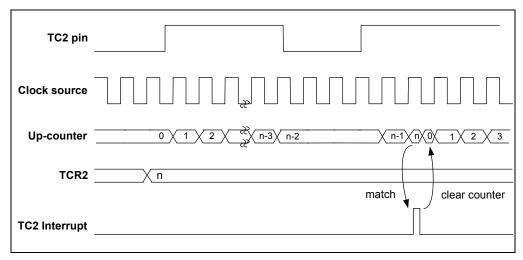

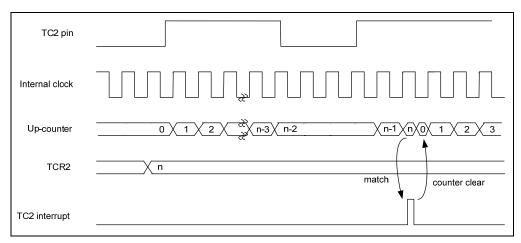

| 6.1.21 | Bank 1 R8 TC2CR (Timer 2 Control)                                             | .25  |

|--------|-------------------------------------------------------------------------------|------|

| 6.1.22 | Bank 1 R9 TC2DH (Timer 2 High Byte Data Buffer)                               | .29  |

| 6.1.23 | Bank 1 RA TC2DL (Timer 2 Low Byte Data Buffer)                                | .29  |

| 6.1.24 | Bank 1 RB SPIS (SPI Status Register)                                          | . 29 |

| 6.1.25 | Bank 1 RC SPIC (SPI Control Register)                                         | .30  |

| 6.1.26 | Bank 1 RD SPIRB (SPI Read Buffer)                                             | .31  |

| 6.1.27 | Bank 1 RE SPIWB (SPI Write Data Buffer)                                       | .32  |

| 6.1.28 | Bank 1 RF (Interrupt Status Register 2)                                       | .32  |

| 6.1.29 | Bank 2 RA URC1 (UART Control 1)                                               | . 32 |

|        | Bank 2 RB URC2 (UART Control 2)                                               |      |

| 6.1.31 | Bank 2 RC URS (UART Status)                                                   | .34  |

| 6.1.32 | Bank 2 RD URRD (UART_RD Data Buffer)                                          | . 35 |

| 6.1.33 | Bank 2 RE URTD (UART_TD Data Buffer)                                          | . 35 |

| 6.1.34 | Bank 2 RF (Pull-high Control Register 1)                                      | . 35 |

|        | Bank 3 R5 (TMRCON: Timer A and Timer B Control Register)                      |      |

|        | Bank 3 R6 (TBHP: Table Pointer Register for Instruction TBRD)                 | . 36 |

| 6.1.37 | Bank 3 R7 (CMPCON: Comparator 2 Control Register and PWMA/B Control Register) | .37  |

| 6.1.38 | Bank 3 R8 (PWMCON: PWMA/B Lower 2 Bits of the Period                          |      |

| 0.4.00 | and Duty Control Register)                                                    |      |

|        | Bank 3 R9 (PRDAH: Most Significant Byte of PWMA)                              |      |

|        | Bank 3 RA (DTAH: Most Significant Byte of PWMA Duty Cycle)                    |      |

|        | Bank 3 RB (PRDBH: Most Significant Byte of PWMB)                              |      |

|        | Bank 3 RC (DTBH: Least Significant Byte of PWMB Duty Cycle)                   |      |

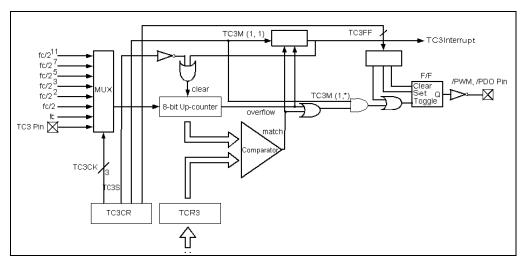

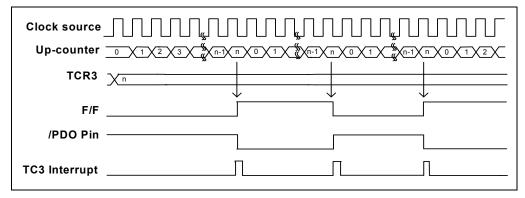

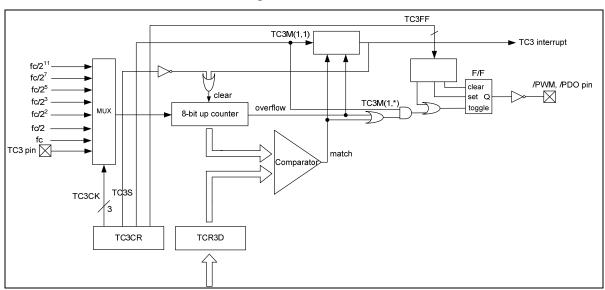

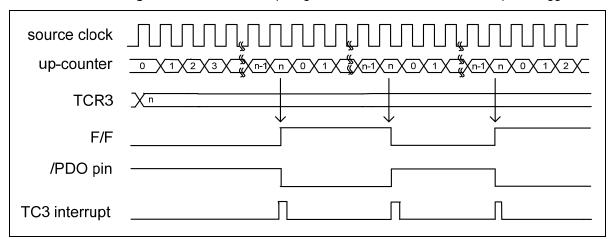

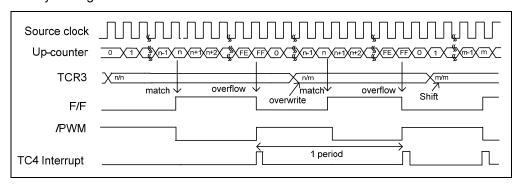

|        | Bank 3 RD TC3CR (Timer 3 Control)                                             |      |

|        | Bank 3 RE TC3D (Timer 3 Data Buffer)                                          |      |

|        | Bank 3 RF (Pull-Down Control Register 1)                                      |      |

| •      | I Function Registers (EM78F644/642/641/544/542/541N Series only) .            |      |

| 6.2.1  | A (Accumulator)                                                               |      |

| 6.2.2  | CONT (Control Register)                                                       |      |

|        | IOC5 (I/O Port 5 Control Register)                                            |      |

|        | IOC6 (I/O Port 6 Control Register)                                            |      |

| 6.2.5  | IOC7 (I/O Port 7 Control Register)                                            |      |

| 6.2.6  | IOC8 (I/O Port 8 Control Register)                                            |      |

| 6.2.7  | IOC9                                                                          |      |

| 6.2.8  | IOCA (WDT Control Register)                                                   |      |

| 6.2.9  | IOCB (Pull-Down Control Register 2)                                           |      |

|        | IOCC (Open-Drain Control Register)                                            |      |

|        | IOCD (Pull-High Control Register 2)                                           |      |

|        | IOCE (Interrupt Mask Register 2)                                              |      |

| 6.2.13 | IOCF (Interrupt Mask Register 1)                                              | .48  |

6.2

| 6.3 | Operat | tional Registers for EM78F648/548N                                   | 49 |

|-----|--------|----------------------------------------------------------------------|----|

|     | 6.3.1  | R0: IAR (Indirect Addressing Register)                               | 49 |

|     | 6.3.2  | R1: BSR (Bank Selection Control Register)                            | 49 |

|     | 6.3.3  | R2: PC (Program Counter)                                             | 49 |

|     | 6.3.4  | R3: SR (Status Register)                                             | 53 |

|     | 6.3.5  | R4: RSR (RAM Select Register)                                        | 54 |

|     | 6.3.6  | Bank 0 R5 ~ R9 (Port 5 ~ Port 9)                                     | 54 |

|     | 6.3.7  | Bank 0 RA (Not Used)                                                 | 54 |

|     | 6.3.8  | Bank 0 RB OMCR (Operating Mode Control Register)                     | 54 |

|     | 6.3.9  | Bank 0 RC: ISR1 (Interrupt Status Register 1)                        | 56 |

|     | 6.3.10 | Bank 0 RD: ISR2 (Interrupt Status Register 2)                        | 57 |

|     | 6.3.11 | Bank 0 RE: ISR3 (Interrupt Status Register 3)                        | 57 |

|     | 6.3.12 | Bank 0 RF                                                            | 58 |

|     | 6.3.13 | Bank 0 R10: EIESCR (External Interrupt Edge Select Control Register) | 58 |

|     | 6.3.14 | Bank 0 R11: WDTCR                                                    | 58 |

|     | 6.3.15 | Bank 0 R12: LVDCR (Low Voltage Detector Control Register)            | 59 |

|     | 6.3.16 | Bank 0 R13: TCCCR (TCC Control Register)                             | 59 |

|     | 6.3.17 | Bank 0 R14: TCCDATA (TCC Data Register)                              | 60 |

|     | 6.3.18 | Bank 0 R15~R19 (IOCR5~IOCR9)                                         | 60 |

|     | 6.3.19 | Bank 0 R1A~R1B                                                       | 60 |

|     | 6.3.20 | Bank 0 R1C: IMR1 (Interrupt Mask Register 1)                         | 60 |

|     | 6.3.21 | Bank 0 R1D: IMR2 (Interrupt Mask Register 2)                         | 61 |

|     | 6.3.22 | Bank 0 R1E: IMR3 (Interrupt Mask Register 3)                         | 62 |

|     | 6.3.23 | Bank 0 R1F                                                           | 62 |

|     | 6.3.24 | Bank 0 R20: P5WUCR (Port 5 Wake Up Control Register)                 | 63 |

|     | 6.3.25 | Bank 0 R21: P5WUECR (Port 5 Wake-up Edge Control Register)           | 63 |

|     | 6.3.26 | Bank 0 R22: P7WUCR (Port 7 Wake-up Control Register)                 | 63 |

|     | 6.3.27 | Bank 0 R23: P7WUECR (Port 7 Wake-up Edge Control Register)           | 63 |

|     | 6.3.28 | Bank 0 R24~R2A                                                       | 63 |

|     | 6.3.29 | Bank 0 R2B: SPICR (SPI Control Register)                             | 64 |

|     | 6.3.30 | Bank0 R2C: SPIS (SPI Status Register)                                | 65 |

|     | 6.3.31 | Bank 0 R2D: SPIR (SPI Read Buffer Register)                          | 65 |

|     | 6.3.32 | Bank 0 R2E: SPIR (SPI Write Buffer Register)                         | 65 |

|     | 6.3.33 | Bank 0 R2F: WUCR1 (Wake-up Control Register 1)                       | 66 |

|     |        | Bank 0 R30~R31                                                       |    |

|     | 6.3.35 | Bank 0 R32: URCR1 (UART Control Register 1)                          | 67 |

|     | 6.3.36 | Bank 0 R33: URCR2 (UART Control Register 2)                          | 67 |

|     | 6.3.37 | Bank 0 R34: URS (UART Status Register)                               | 68 |

|     | 6.3.38 | Bank 0 R35: URRD (UART Receive Data Buffer Register)                 | 69 |

|     | 6.3.39 | Bank 0 R36: URTD (UART Transmit Data Buffer Register)                | 69 |

|     | 6.3.40 | Bank 0 R37: TBPTL (Table Pointer Low Register)                       | 69 |

|     | 6.3.41 | Bank 0 R38: TBPTH (Table Pointer High Register)                      | 69 |

| 6.3.42 | Bank 0 R39: CMP1CR (Comparator 1 Control Register)                          | 69 |

|--------|-----------------------------------------------------------------------------|----|

| 6.3.43 | Bank 0 R3A~R3B                                                              | 70 |

| 6.3.44 | Bank 0 R3C: CMP2CR (Comparator 2 Control Register)                          | 71 |

| 6.3.45 | Bank 0 R3D~R42                                                              | 72 |

| 6.3.46 | Bank 0 R43: CPIRLCON (Comparator Internal Reference Level Control Register) | 72 |

| 6.3.47 | Bank 0 R44~R47                                                              | 72 |

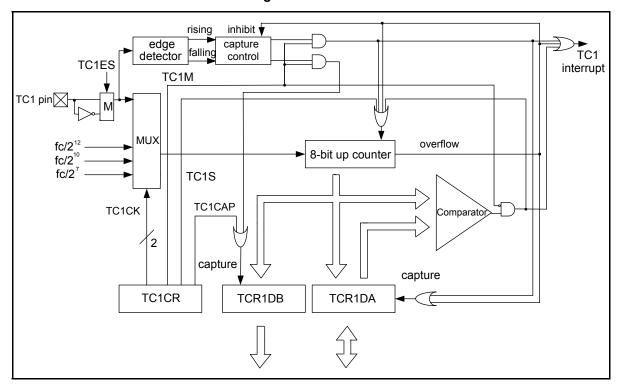

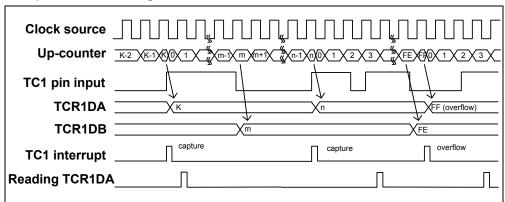

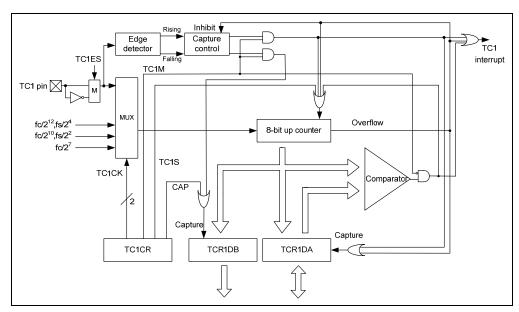

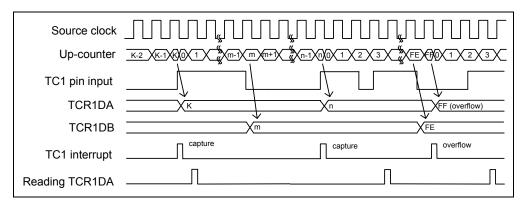

| 6.3.48 | Bank 0 R48: TC1CR (Timer 1 Control Register)                                | 72 |

| 6.3.49 | Bank 0 R49: TCR1DA (Timer 1 Data Buffer A)                                  | 75 |

| 6.3.50 | Bank 0 R4A: TCR1DB (Timer 1 Data Buffer B)                                  | 75 |

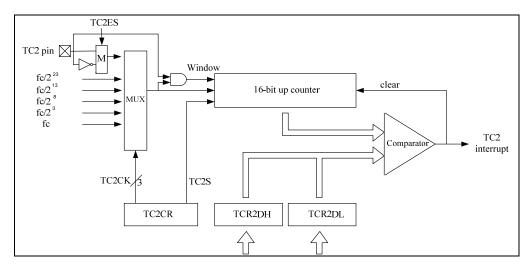

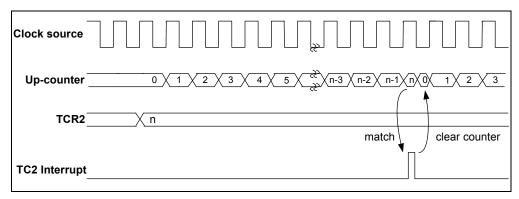

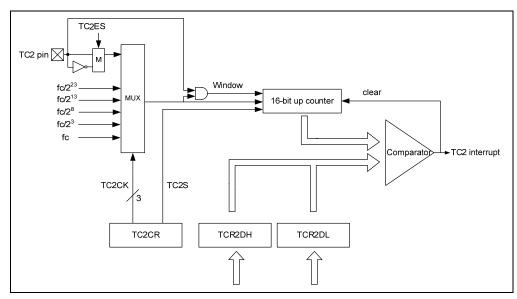

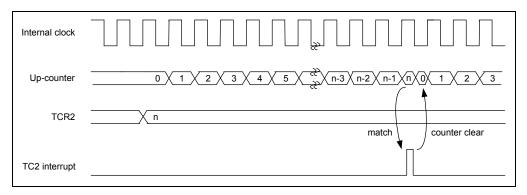

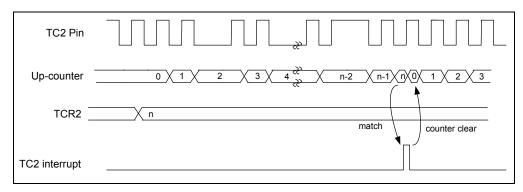

| 6.3.51 | Bank 0 R4B: TC2CR (Timer 2 Control Register)                                | 75 |

| 6.3.52 | Bank 0 R4C: TCR2DH (Timer 2 High Byte Data Buffer Register)                 | 77 |

| 6.3.53 | Bank 0 R4D: TCR2DL (Timer 2 Low Byte Data Buffer Register)                  | 78 |

| 6.3.54 | Bank 0 R4E: TC3CR (Timer 3 Control Register)                                | 78 |

| 6.3.55 | Bank 0 R4F: TCR3D (Timer 3 Duty Buffer Register)                            | 80 |

| 6.3.56 | Bank 1 R5: P5PHCR (Port 5 Pull High Control Register)                       | 80 |

| 6.3.57 | Bank 1 R6: P6PHCR (Port 6 Pull High Control Register)                       | 81 |

| 6.3.58 | Bank 1 R7: P7PHCR (Port 7 Pull High Control Register)                       | 81 |

| 6.3.59 | Bank 1 R8: P8PHCR (Port 8 Pull High Control Register)                       | 81 |

| 6.3.60 | Bank 1 R9: P9PHCR (Port 9 Pull High Control Register)                       | 82 |

| 6.3.61 | Bank 1 RA                                                                   | 82 |

| 6.3.62 | Bank 1 RB: P5PLCR (Port 5 Pull Low Control Register)                        | 82 |

| 6.3.63 | Bank 1 RC: P6PLCR (Port 6 Pull Low Control Register)                        | 83 |

| 6.3.64 | Bank 1 RD: P7PLCR (Port 7 Pull Low Control Register)                        | 83 |

| 6.3.65 | Bank 1 RE: P8PLCR (Port 8 Pull Low Control Register)                        | 84 |

| 6.3.66 | Bank 1 RF: P9PLCR (Port 9 Pull Low Control Register)                        | 84 |

| 6.3.67 | Bank 1 R10                                                                  | 84 |

| 6.3.68 | Bank 1 R11: P5HD/SCR (Port 5 High Drive/Sink Control Register)              | 84 |

| 6.3.69 | Bank 1 R12: P6HD/SCR (Port 6 High Drive/Sink Control Register)              | 85 |

| 6.3.70 | Bank 1 R13: P7HD/SCR (Port 7 High Drive/Sink Control Register)              | 85 |

| 6.3.71 | Bank 1 R14: P8HD/SCR (Port 8 High Drive/Sink Control Register)              | 85 |

| 6.3.72 | Bank 1 R15: P9HD/SCR (Port 9 High Drive/Sink Control Register)              | 85 |

| 6.3.73 | Bank 1 R16                                                                  | 85 |

| 6.3.74 | Bank 1 R17: P5ODCR (Port 5 Open Drain Control Register)                     | 86 |

| 6.3.75 | Bank 1 R18: P6ODCR (Port 6 Open Drain Control Register)                     | 86 |

| 6.3.76 | Bank 1 R19: P7ODCR (Port 7 Open Drain Control Register)                     | 86 |

| 6.3.77 | Bank 1 R1A: P8ODCR (Port 8 Open Drain Control Register)                     | 86 |

| 6.3.78 | Bank 1 R1B: P9ODCR (Port 9 Open Drain Control Register)                     | 86 |

| 6.3.79 | Bank 1 R1C                                                                  | 87 |

| 6.3.80 | Bank 1 R1D: IRCS (IRC Frequency Selection Register)                         | 87 |

| 6.3.81 | Bank 1 R1E                                                                  | 87 |

| 6.3.82 | Bank 1 R1F: EEPROM Control                                                  | 87 |

| 6.3.83    | Bank 1 R20: EEPROM ADDR                                       | 88 |

|-----------|---------------------------------------------------------------|----|

| 6.3.84    | Bank 1 R21: EEPROM DATA                                       | 88 |

| 6.3.85    | Bank1 R22                                                     | 88 |

| 6.3.86    | Bank1 R23: I2CCR1 (I2C Status and Control Register 1)         | 88 |

| 6.3.87    | Bank 1 R24: I2CCR2 (I2C Status and Control Register2)         | 89 |

| 6.3.88    | Bank 1 R25: I2CSA (I2C Slave Address Register)                | 90 |

| 6.3.89    | Bank 1 R26: I2CDA (I2C Device Address Register)               | 90 |

| 6.3.90    | Bank 1 R27: I2CDB (I2C Data Buffer Register)                  |    |

| 6.3.91    | Bank 1 R28: I2CA (I2C Data Buffer Register)                   | 91 |

| 6.3.92    | Bank 1 R29                                                    |    |

| 6.3.93    | Bank 1 R2A: PWMER (PWM Enable Control Register)               | 91 |

| 6.3.94    | Bank 1 R2B: TIMEN (Timer/PWM Enable Control Register)         | 91 |

| 6.3.95    | Bank 1 R2C~R2E                                                |    |

| 6.3.96    | Bank 1 R2F: PWMACR (PWM A Control Register)                   |    |

| 6.3.97    | Bank 1 R30: PWMBCR (PWM B Control Register)                   |    |

| 6.3.98    | Bank 1 R31                                                    |    |

| 6.3.99    | Bank 1 R32: TACR (Timer A Control Register)                   |    |

| 6.3.100   | Bank1 R33: TBCR (Timer B Control Register)                    |    |

| 6.3.101   | Bank 1 R34                                                    |    |

| 6.3.102   | Bank 1 R35: TAPRDH (Timer A Period Buffer Register)           |    |

| 6.3.103   | Bank 1 R36: TBPRDH (Timer B Period Buffer Register)           |    |

| 6.3.104   | Bank 1 R37                                                    |    |

| 6.3.105   | Bank 1 R38: TADTH (Timer A Duty Buffer Register)              |    |

| 6.3.106   | Bank 1 R39: TBDTH (Timer B Duty Buffer Register)              |    |

| 6.3.107   | Bank1 R3A                                                     |    |

| 6.3.108   | Bank 1 R3B: PRDxL (PWM A/B/C Period Buffer Low Bits Register) |    |

| 6.3.109   | ,                                                             |    |

| 6.3.110   |                                                               |    |

| 6.3.111   | Bank 0 R50~R7F, Bank0~1 R80~RFF                               |    |

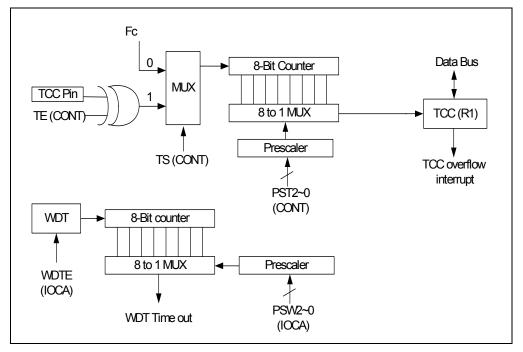

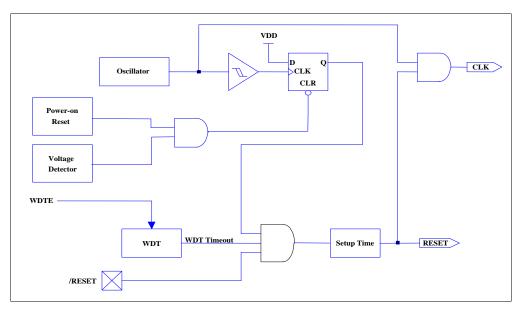

| TCC/WE    | OT and Prescaler                                              | 94 |

| I/O Ports | <b>3</b>                                                      | 95 |

| 6.5.1 L   | O for EM78F644N/642/641/544/542/541N                          | 95 |

| 6.5.2 L   | O for EM78F648/548N                                           | 96 |

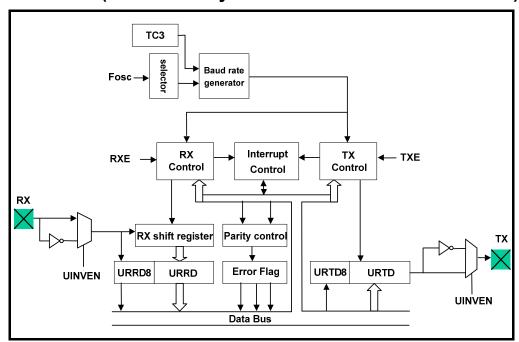

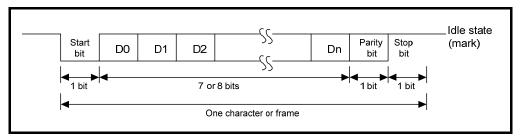

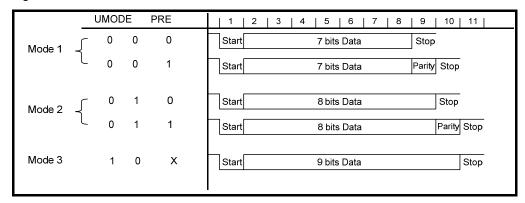

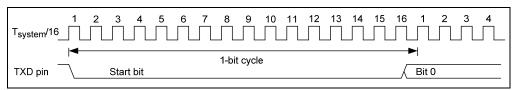

| UART (L   | Jniversal Asynchronous Receiver/Transmitter)                  | 97 |

| •         | JART Mode                                                     |    |

|           | ransmitting                                                   |    |

|           | Receiving                                                     |    |

|           | Baud Rate Generator                                           |    |

|           | JART Timing                                                   |    |

| 0.0.0     | // u.v.   mmg                                                 | 0  |

6.4 6.5

6.6

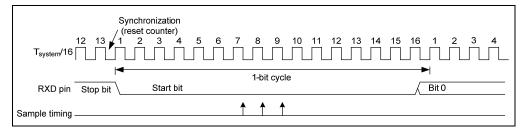

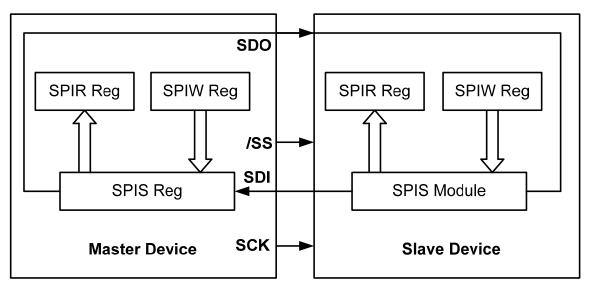

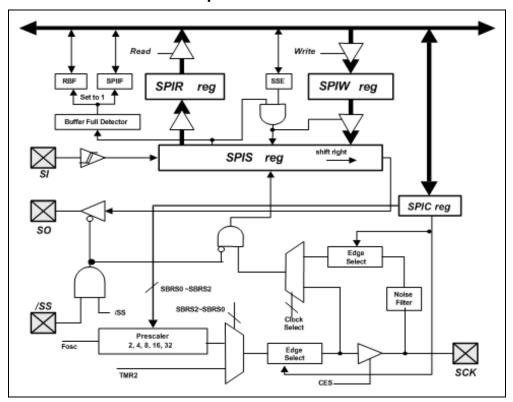

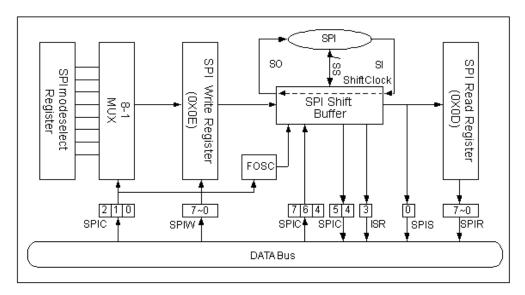

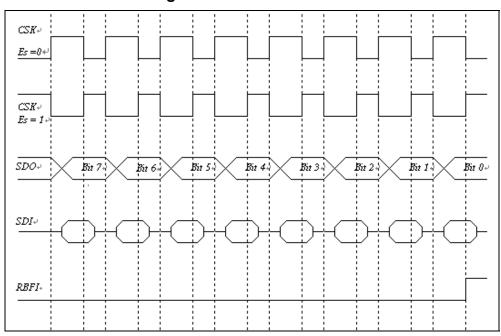

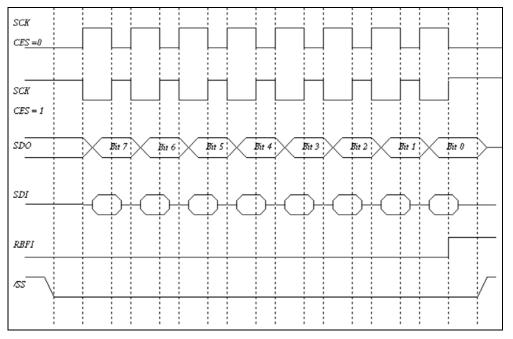

| 6.7  | SPI Fu | nction                                                                                             | 100 |

|------|--------|----------------------------------------------------------------------------------------------------|-----|

|      | 6.7.1  | Overview and Features                                                                              | 100 |

|      |        | 6.7.1.1 Overview                                                                                   | 100 |

|      |        | 6.7.1.2 Features                                                                                   | 100 |

|      | 6.7.2  | SPI Function Description                                                                           | 102 |

|      | 6.7.3  | SPI Signal and Pin Description                                                                     | 103 |

|      | 6.7.4  | SPI Mode Timing                                                                                    | 105 |

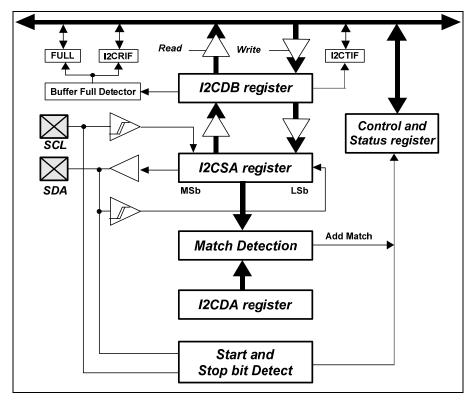

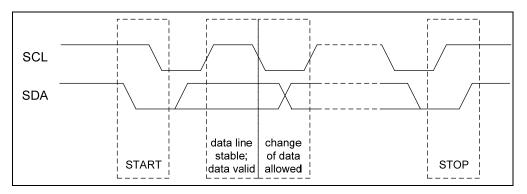

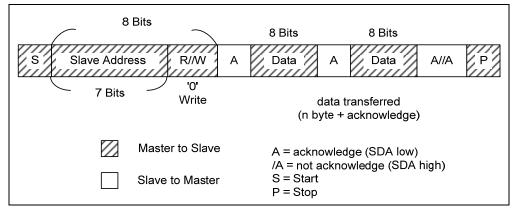

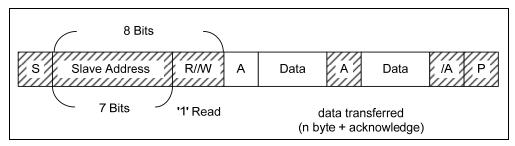

| 6.8  | I2C Fu | nction                                                                                             | 106 |

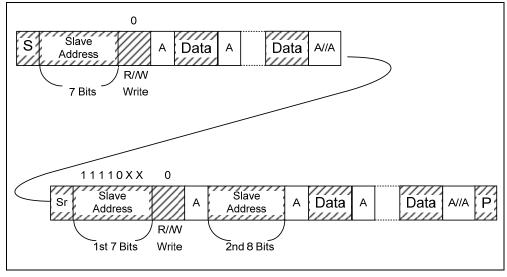

|      | 6.8.1  | 7-Bit Slave Address                                                                                | 108 |

|      | 6.8.2  | 10-Bit Slave Address                                                                               | 108 |

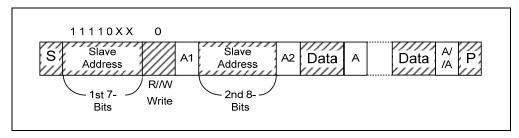

|      |        | 6.8.2.1 Master-Transmitter Transmits to Slave-Receiver with a 10-bit Slave Address                 | 109 |

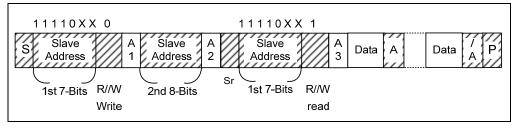

|      |        | 6.8.2.2 Master-Receiver Reads from Slave-Transmitter with a 10-bit Slave Address                   | 109 |

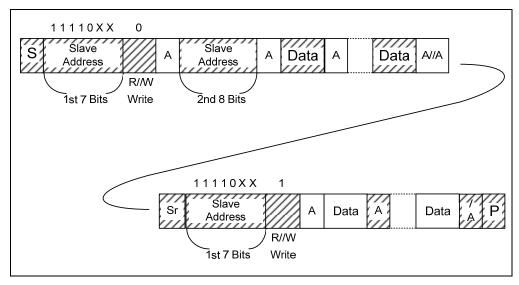

|      |        | 6.8.2.3 Master Transmits and Receives Data to and from the Same Slave Device with 10-Bit Addresses | 110 |

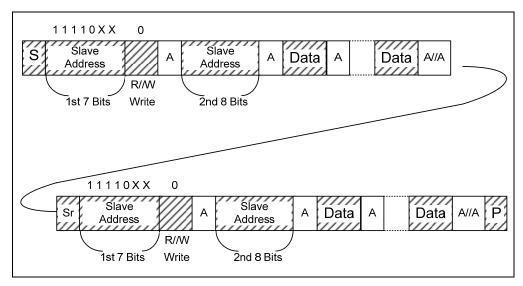

|      |        | 6.8.2.4 Master Device Transmits Data to Two or More                                                |     |

|      |        | Slave Devices with 10 and 7 Bits Slave Address                                                     |     |

|      | 6.8.3  | Master Mode I2C Transmit                                                                           |     |

|      | 6.8.2  | Slave Mode I2C Transmit                                                                            |     |

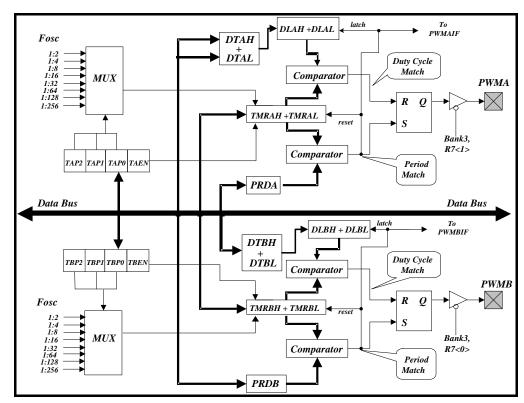

| 6.9  |        | et of PWM (Pulse Width Modulation)                                                                 |     |

|      | 6.9.1  | Overview                                                                                           |     |

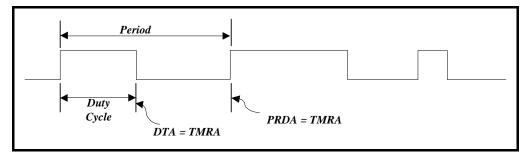

|      | 6.9.2  | Increment Timer Counter (TMRX: TMRAH/L or TMRBH/L)                                                 |     |

|      | 6.9.3  | PWM Period (PRDX: PRDA or PRDB)                                                                    |     |

| 0.40 | 6.9.4  | PWM Duty Cycle (DTX: DTA or DTB)                                                                   |     |

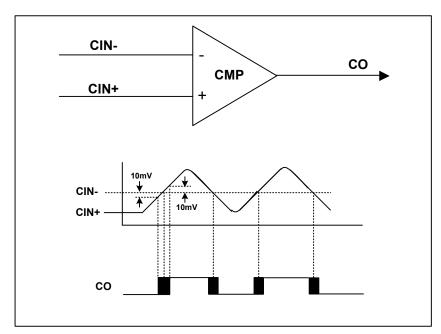

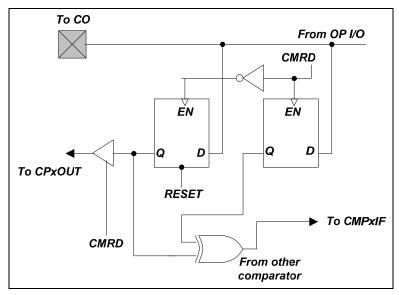

| 6.10 | •      | arator                                                                                             |     |

|      |        | External Reference Signal                                                                          |     |

|      |        | Internal Reference Signal                                                                          |     |

|      |        | Comparator Outputs                                                                                 |     |

|      |        | Interrupt                                                                                          |     |

|      |        | Wake-up from Sleep Mode                                                                            |     |

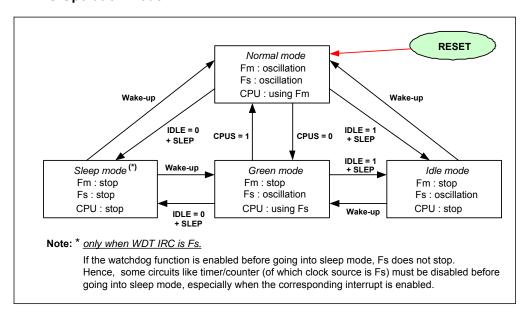

| 6.11 |        | and Wake-up                                                                                        |     |

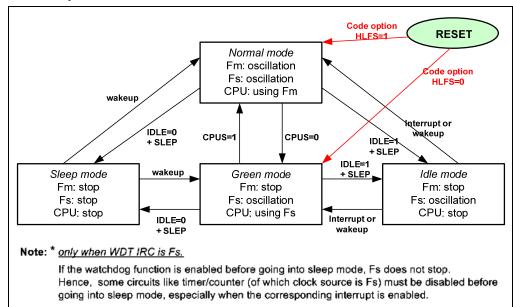

|      |        | Reset and Wake-up for EM78F644/642/641/544/542/541N                                                |     |

|      |        | Reset and Wake-up for EM78F648/548N                                                                |     |

|      |        | The Status of RST, T, and P of STATUS Register                                                     |     |

| 6.12 |        | pt                                                                                                 |     |

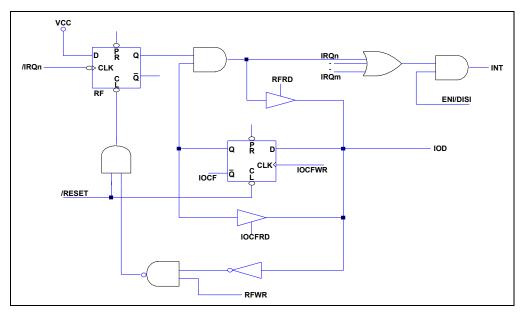

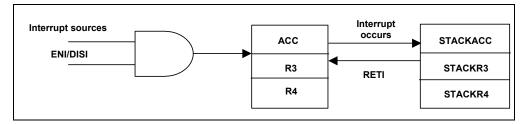

|      |        | Interrupt for EM78F644/642/641/544/542/541N                                                        |     |

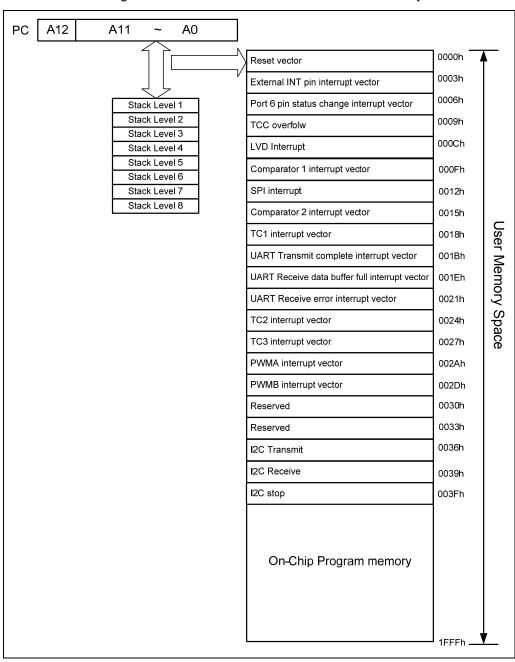

|      |        | Interrupt for EM78F648/548N                                                                        |     |

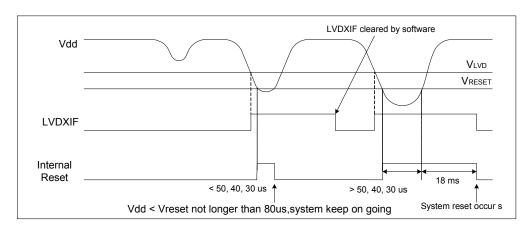

| 6.13 | •      | ow Voltage Detector) for EM78F648/548N                                                             |     |

|      |        | LVD Level Control                                                                                  |     |

|      |        | LVD Interrupt                                                                                      |     |

|      | 6.13.3 | LVD Function Setup                                                                                 | 148 |

|   | 6.14 | Data E  | EPROM                                                                                                  | 150 |

|---|------|---------|--------------------------------------------------------------------------------------------------------|-----|

|   | 6.15 | Oscilla | ator                                                                                                   | 150 |

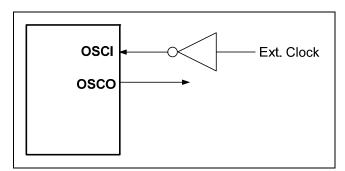

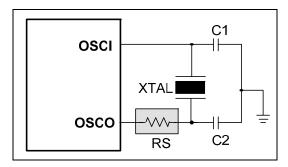

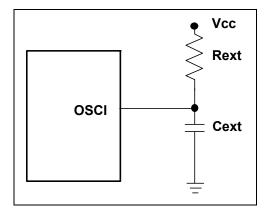

|   |      | 6.15.1  | Oscillator Modes                                                                                       | 150 |

|   |      | 6.15.2  | Crystal Oscillator/Ceramic Resonators (XTAL)                                                           | 151 |

|   |      |         | External RC Oscillator Mode                                                                            |     |

|   |      | 6.15.4  | Internal RC Oscillator Mode                                                                            | 153 |

|   | 6.16 | Power   | on Considerations                                                                                      | 154 |

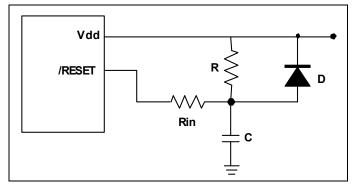

|   | 6.17 | Extern  | al Power-on Reset Circuit                                                                              | 154 |

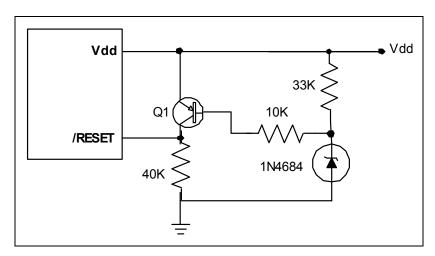

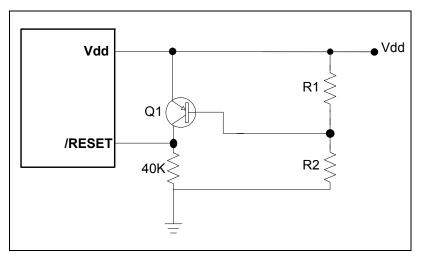

|   | 6.18 | Residu  | ue-Voltage Protection                                                                                  | 155 |

|   | 6.19 | Code    | Option Register                                                                                        | 156 |

|   |      | 6.19.1  | Code Option Register (Word 0)                                                                          | 156 |

|   |      |         | 6.19.1.1 EM78F644/642/641/544/542/541N Code Option Word 0                                              |     |

|   |      |         | 6.19.1.1 EM78F648/548 Code Option Word 0                                                               |     |

|   |      | 6.19.2  | Code Option Register (Word 1)                                                                          |     |

|   |      |         | 6.19.2.1 EM78F644/642/641/544/542/541N Code Option Word 1<br>6.19.2.2 EM78F648/548N Code Option Word 1 |     |

|   |      | 6 10 3  | Customer ID Register (Word 2)                                                                          |     |

|   |      | 0.19.5  | 6.19.3.1 EM78F644/642/641/544/542/541N Code Option Word 2                                              |     |

|   |      |         | 6.19.3.2 EM78F648/548N Code Option Word 2                                                              |     |

|   | 6.20 | Instruc | ction Set                                                                                              |     |

|   |      | 6.20.1  | Instruction Set Table                                                                                  | 162 |

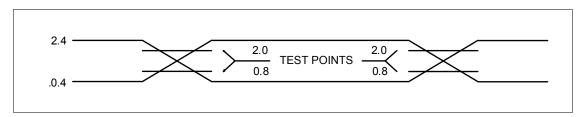

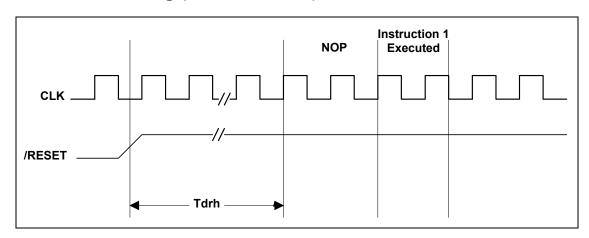

| 7 | Timi |         | gram                                                                                                   |     |

|   | 7.1  | _       | st Input/Output Waveform                                                                               |     |

|   | 7.2  |         | Timing (CLK1:0 = "01")                                                                                 |     |

| 8 | Abso |         | laximum Ratings                                                                                        |     |

| • |      |         | M78F648/548N                                                                                           |     |

| 9 |      |         | al Characteristics                                                                                     |     |

| 9 |      |         |                                                                                                        |     |

|   | 9.1  |         | M78F648/548N                                                                                           |     |

|   |      | 9.1.1   | Program Flash Memory Electrical Characteristics (for EM78E649N only)                                   |     |

|   |      | 9.1.2   | Data EEPROM Electrical Characteristics (for EM78F648N only)  Comparator Electrical Characteristics     |     |

|   | 9.2  |         | M78F644/544N                                                                                           |     |

|   | 9.2  | 9.2.1   | Program Flash Memory Electrical Characteristics                                                        |     |

|   |      | 9.2.1   | Data EEPROM Electrical Characteristics (for EM78F644N only)                                            |     |

|   |      | 9.2.3   | Comparator Electrical Characteristics (ISF ENT OF 6441 Only)                                           |     |

|   | 9.3  |         | F642/542N                                                                                              |     |

|   | 5.5  | 9.3.1   | Program Flash Memory Electrical Characteristics                                                        |     |

|   |      | 9.3.2   | Data EEPROM Electrical Characteristics (for EM78F642N only)                                            |     |

|   |      | 9.3.3   | Comparator Electrical Characteristics                                                                  |     |

|   |      |         |                                                                                                        | _   |

|    | 9.4        | EM78F    | 641/541N                                                    | 176 |

|----|------------|----------|-------------------------------------------------------------|-----|

|    |            | 9.4.1    | Program Flash Memory Electrical Characteristics             | 178 |

|    |            | 9.4.2    | Data EEPROM Electrical Characteristics (for EM78F641N only) | 178 |

|    |            | 9.4.3    | Comparator Electrical Characteristics                       | 178 |

| 10 | AC I       | Electric | cal Characteristics                                         | 179 |

|    | 10 1       | FM78     | F648/548N                                                   | 179 |

|    |            |          | F644/642/641/544/542/541N                                   |     |

|    |            |          |                                                             |     |

|    |            |          |                                                             |     |

|    |            |          | APPENDIX                                                    |     |

| Α  | Pac        |          | /pe                                                         |     |

|    | A.1        | Green    | Products Compliance                                         | 180 |

| В  | Pac        | kaging   | Configuration                                               | 181 |

|    | B.1        | EM78     | F648/548N                                                   | 181 |

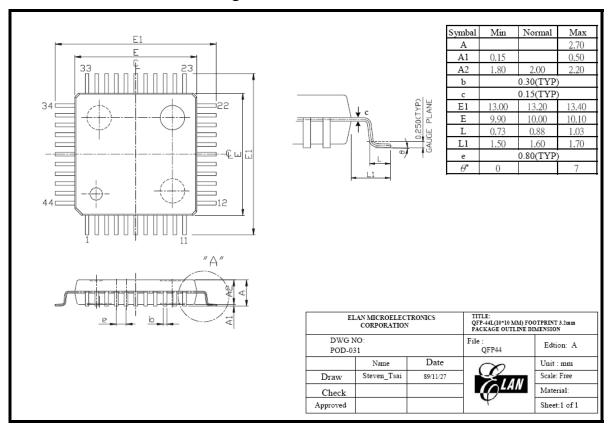

|    |            | B.1.1    | 44-Pin QFP Package                                          | 181 |

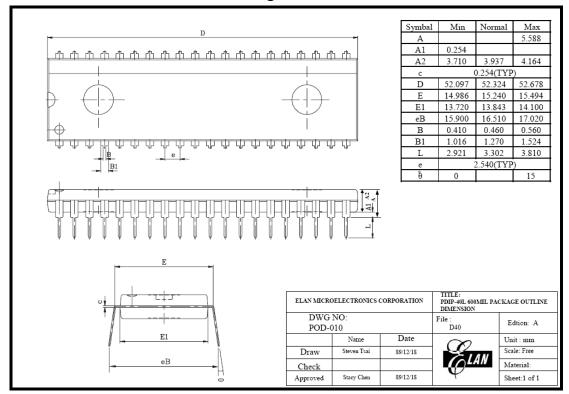

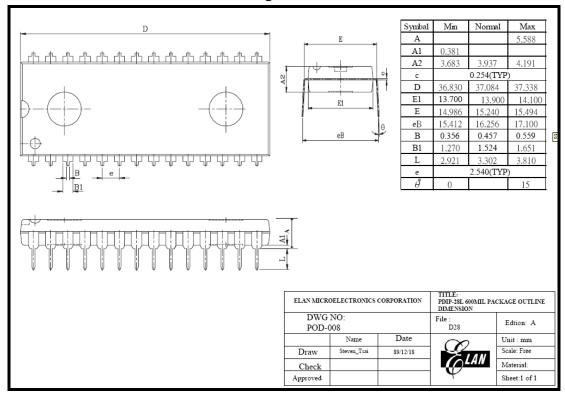

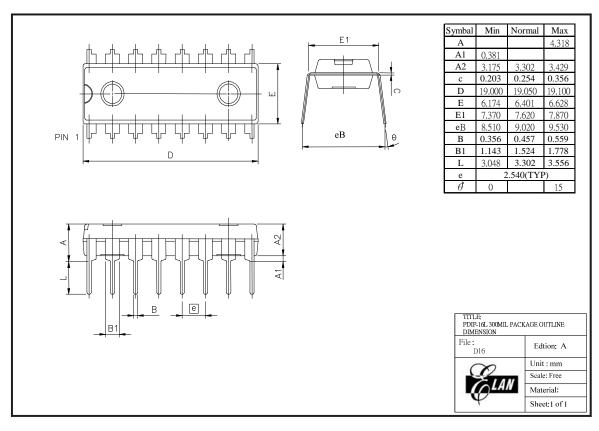

|    |            | B.1.2    | 40-Pin DIP Package                                          | 182 |

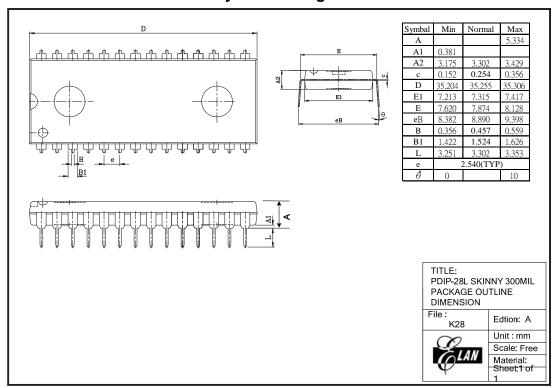

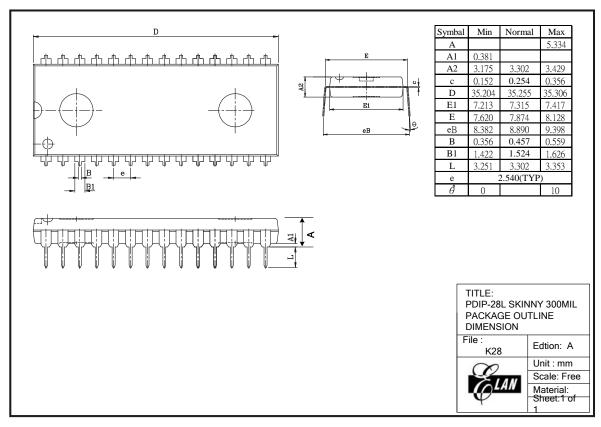

|    |            | B.1.3    | 28-Pin Skinny DIP Package                                   | 183 |

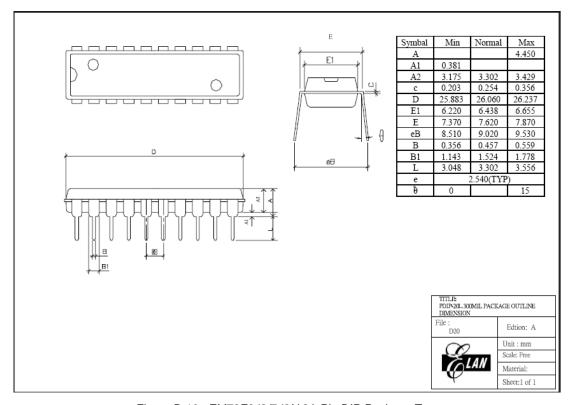

|    |            | B.1.4    | 28-Pin DIP Package                                          | 184 |

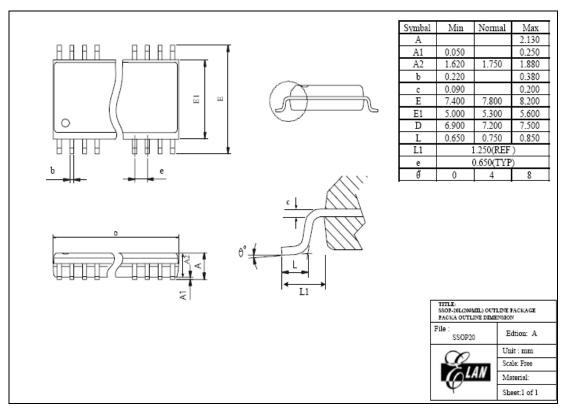

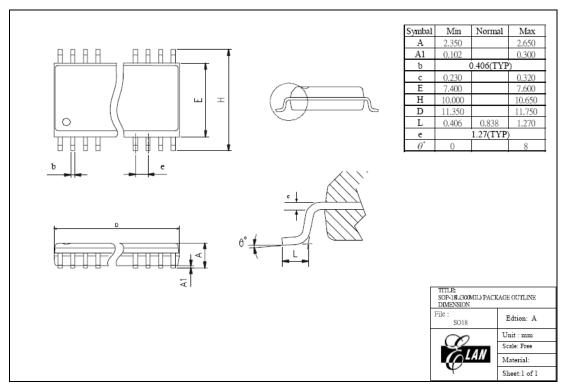

|    |            | B.1.5    | 28-Pin SOP Package                                          | 185 |

|    | B.2        | EM78     | F644/544N                                                   | 186 |

|    |            | B.2.1    | 28-Pin Skinny DIP Package                                   | 186 |

|    |            | B.2.2    | 28-Pin SOP Package                                          |     |

|    |            | B.2.3    | 24-Pin Skinny DIP Package                                   |     |

|    |            | B.2.4    | 24-Pin SOP Package                                          |     |

|    | B.3        | EM78     | F642/542N                                                   |     |

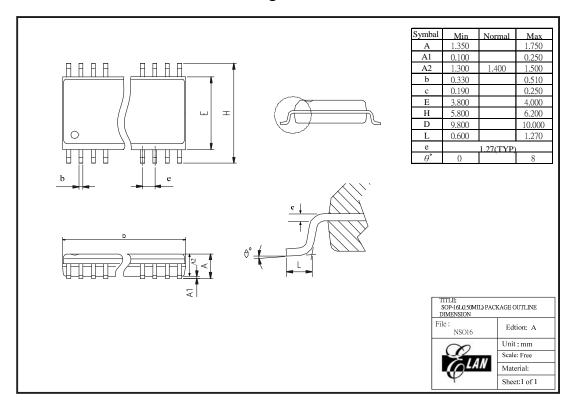

|    |            | B.3.1    | 20-Pin DIP Package                                          |     |

|    |            | B.3.2    | <b>G</b>                                                    |     |

|    |            | B.3.3    | 20-Pin SSOP Package                                         |     |

|    |            | B.3.4    | 18-Pin DIP Package                                          |     |

|    | <b>-</b> . | B.3.5    | 18-Pin SOP Package                                          |     |

|    | B.4        |          | F641/541N                                                   |     |

|    |            | B.4.1    | 16-Pin DIP Package                                          |     |

|    |            | B.4.2    | 16-Pin SOP Package                                          |     |

| _  | _          | B.4.3    | 10-Pin MSOP Package                                         |     |

| С  |            | -        | surance and Reliability                                     |     |

|    | C.1        | Addre    | ss Trap Detect                                              | 198 |

## **Specification Revision History**

| Doc. Version | Revision Description                                                                                                                                                                                                                                                                                                                                                                                   | Date       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.0          | Initial release version                                                                                                                                                                                                                                                                                                                                                                                | 2010/05/05 |

| 1.1          | <ol> <li>Modified the contents of the Operating Frequency<br/>Range vs. Operating Voltage in Section 2 Features</li> <li>Modified the description of the Control-bit TS.</li> <li>Modified the descriptions in the Section TCC/WDT and<br/>Prescaler.</li> <li>Modified Figure 6-11 TCC and WDT Block Diagram.</li> <li>Modified the maximum supportable baud rate of the<br/>SPI function.</li> </ol> | 2012/07/17 |

| 1.2          | <ol> <li>Modified the pin number of EM78F641/541N in<br/>Figure 3-4</li> <li>Added LVR specification in the DC Electrical<br/>Characteristics section.</li> </ol>                                                                                                                                                                                                                                      | 2013/03/15 |

## 1 General Description

The EM78F64xN/54xN Series are 8-bit microprocessors designed and developed with low-power, high-speed CMOS technology, and high noise immunity. Each of these MUCs are equipped with on-chip 1/2/4K×13-bit and 8Kx15-bit Electrical Flash Memory, but only the EM78F64xN are embedded with 256 or 128×8-bit in-system programmable EEPROM. Each provides three protection bits to prevent intrusion of user's Flash memory code. Twelve Code option bits are also available to meet user's requirements.

With its enhanced Flash-ROM features, the EM78F64xN/54xN MUCs provide a convenient way of developing and verifying user's programs. Moreover, the Flash-ROM device offers the advantages of easy and effective program updates with development and programming tools. Users can take advantage of ELAN's Writer to easily program their development codes.

## 2 Features

## ■ CPU Configuration

| CPU    | EM78F648N<br>EM78F548N     |                          |                          | EM78F641N<br>EM78F541N   |

|--------|----------------------------|--------------------------|--------------------------|--------------------------|

| ROM    | 8K × 15 bits               | 4K × 13 bits             | 2K × 13 bits             | 1K × 13 bits             |

| SRAM   | 304 × 8 bits               | 144 × 8 bits             | 80 × 8 bits              | 48 × 8 bits              |

| EEPROM | 256 bytes<br>(648N only)   | 256 bytes<br>(644N only) | 128 bytes<br>(642N only) | 128 bytes<br>(641N only) |

| STACK  | 8-Level                    | 8-Level                  | 8-Level                  | 8-Level                  |

| LVR    | 4.2, 3.7, 2.7V             | 4.0, 3.5, 2.7V           | 4.0, 3.5, 2.7V           | 4.0, 3.5, 2.7V           |

| LVD    | 2.3 / 3.3 / 4.0<br>/ 4.5 V | х                        | х                        | х                        |

- In-system programmable EEPROM Endurance: 1,000,000 write/erase cycles

- More than 10 years data retention

- Less than 1.5 mA at 5V / 4 MHz

- Typically 20 μA, at 3V / 32kHz

- Typically 1.5 μA, during Sleep mode

## ■ I/O Port Configuration

| I/O           |             | EM78F644N |            |            |

|---------------|-------------|-----------|------------|------------|

| Port          | EMI/8F548N  | EM78F544N | EMI/8F54ZN | EMI/8F54TN |

| I/O           | P5, P6, P7, | P5, P6,   | P5, P6,    | P5, P6,    |

|               | P8, P9      | P7, P8    | P7, P8     | P8         |

| Pull-<br>High | 40          | 14        | 10         | 6          |

| Pull-         |             |           |            |            |

| Down          | 40          | 14        | 7          | 5          |

| Open-         | 40          |           |            | •          |

| drain         | 40          | 8         | 8          | 6          |

| High          |             |           |            |            |

| Sink          | 40          | Х         | Х          | Х          |

| High<br>Sink  | 40          | x         | х          | х          |

- Wake-up port: P6

- External interrupt with Wake-up: P60

## Operating Frequency Range (Base On Two Clocks)

| Operating    | EM78F648N   | EM78F644N   | EM78F642N   | EM78F641N   |

|--------------|-------------|-------------|-------------|-------------|

| Frequency    | EM78F548N   | EM78F544N   | EM78F542N   | EM78F541N   |

|              | DC ~ 4 MHz  | DC ~ 4 MHz  | DC~ 4 MHz   | DC ~ 4 MHz  |

| Crystal Mode | 2.4 ~ 5.5V  | 2.3 ~ 5.5V  | 2.2 ~ 5.5V  | 2.2 ~ 5.5V  |

| *            | DC ~ 8 MHz  |

| ERC Mode     | 3 ~ 5.5V    | 3 ~ 5.5V    | 3 ~ 5.5V    | 3 ~ 5.5V    |

| IRC Mode     | DC ~ 20 MHz | DC ~ 16 MHz | DC ~ 16 MHz | DC ~ 16 MHz |

|              | 5 ~ 5.5V    | 4.5 ~ 5.5V  | 4.5 ~ 5.5V  | 4.5 ~ 5.5V  |

## Available Interrupts

| Interrupt | EM78F648N<br>EM78F548N |    |   |   |

|-----------|------------------------|----|---|---|

| Internal  | 15                     | 10 | 4 | 2 |

| External  | 4                      | 3  | 3 | 3 |

## ■ Peripheral Configuration

| Function                             |                   |                            |                | EM78F641N<br>EM78F541N |

|--------------------------------------|-------------------|----------------------------|----------------|------------------------|

| Two channel PWM                      | 10-bit resolution | 10-bit resolution          | x              | x                      |

| One 8-bit                            | Timer             | Timer                      | Timer          | х                      |

| Timer/counter                        | Counter           | Counter                    | Counter        |                        |

| (TC1)                                | Capture           | Capture                    | Capture        |                        |

| One 16-bit<br>Timer/counter<br>(TC2) | Timer             | Timer<br>Counter<br>Window | Timer          | х                      |

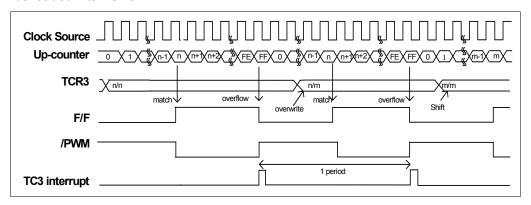

| One 8-bit                            | Timer             | Timer                      | Timer          | Timer                  |

| Timer/counter                        | Counter           | Counter                    | Counter        | Counter                |

| (TC3)                                | PWM / PDO         | PWM / PDO                  | PWM / PDO      | PWM / PDO              |

| One-set                              | 10mv              | 10mv                       | 5mv            | 5mv                    |

| Comparator                           | offset voltage    | offset voltage             | offset voltage | offset voltage         |

- 8-bit real time clock/counter (TCC) with selective signal sources, trigger edges, and overflow interrupt

- External interrupt input pin

- 2-/4-/8-/16 clocks per instruction cycle selected by code option

## ■ Operating Voltage Range

|                       | EM78F648N<br>EM78F548N |            |            |            |

|-----------------------|------------------------|------------|------------|------------|

| Commercial 0°C~70°C   | 2.4 ~ 5.5V             | 2.2 ~ 5.5V | 2.2 ~ 5.5V | 2.2 ~ 5.5V |

| Industrial -40°C~85°C | 2.6 ~ 5.5V             | 2.4 ~ 5.5V | 2.4 ~ 5.5V | 2.4 ~ 5.5V |

## ■ Communciation Peripheral Configuration

| Function |                        | EM78F644N<br>EM78F544N |   |   |  |

|----------|------------------------|------------------------|---|---|--|

| SPI      | Three wire synchronous | Three wire synchronous | x | х |  |

|          | communication          | communication          |   |   |  |

|          | Two wire               | Two wire               |   |   |  |

| UART     | Asynchronous           | Asynchronous           | х | х |  |

|          | communication          | communication          |   |   |  |

|          | 7 / 10 bits            |                        |   |   |  |

| I2C      | Address &              | x                      | х | х |  |

|          | 8 bits data            |                        |   |   |  |

#### ■ Internal RC Drift Rate

|                          | Drift Rate               |      |         |         |  |  |  |  |  |

|--------------------------|--------------------------|------|---------|---------|--|--|--|--|--|

| Internal RC<br>Frequency | Temperature (-40°C~85°C) | _    | Process | Total   |  |  |  |  |  |

| 4 MHz                    | ± 3%                     | ± 5% | ± 2.5%  | ± 10.5% |  |  |  |  |  |

| 16 MHz                   | ± 3%                     | ± 5% | ± 2.5%  | ± 10.5% |  |  |  |  |  |

| 8 MHz                    | ± 3%                     | ± 5% | ± 2.5%  | ± 10.5% |  |  |  |  |  |

| *455kHz                  | ± 3%                     | ± 5% | ± 2.5%  | ± 10.5% |  |  |  |  |  |

<sup>\*</sup>NOT applicable to EM78F541N and EM78F641N

## • Power down (Sleep) mode

• High EFT immunity

## Special Features

- Programmable free running Watchdog Timer

- Power-on voltage detector available (2.0V ~ 2.1V)

#### ■ EM78F648N/548N Package Types

44-pin QFP 10x10 mm: EM78Fx48NQ44J/S

40-pin DIP 600 mil: EM78Fx48ND40J/S

28-pin SKDIP 300 mil: EM78Fx48NK28J/S

28-pin SOP 300 mil: EM78Fx48NSO28J/S

## ■ EM78F644N/544N Package Types

28-pin SKDIP 300 mil : EM78Fx44NK28J/S

28-pin SOP 300 mil : EM78Fx44NSO28J/S

24-pin SKDIP 300 mil : EM78Fx44NK24J/S

24-pin SOP 300 mil : EM78Fx44NSO24J/S

## ■ EM78F642N/542N Package Types

20-pin DIP 300 mil

20-pin SOP 300 mil

EM78Fx42ND20J/S

20-pin SOP 209 mil

EM78Fx42NSO20J/S

18-pin DIP 300 mil

EM78Fx42NSS20J/S

EM78Fx42ND18J/S

EM78Fx42NSO20J/S

## ■ EM78F641N/541N Package Types

• 16-pin DIP 300 mil : EM78Fx41NAD16J/S

16-pin SOP 150 mil

EM78Fx41NASO16J/S

• 10-pin MSOP 118 mil : EM78Fx41NMS10J/S

#### **NOTE**

These are Green Products which do not contain hazardous substances.

## 2.1 Features Selection Guide

| Part No.  | VDD           | Program<br>Memory | Data<br>Memory  |    | 8- | ner<br>16- |                      | UART                               | SPI                                   | I2C                                     | Package<br>Type                  |

|-----------|---------------|-------------------|-----------------|----|----|------------|----------------------|------------------------------------|---------------------------------------|-----------------------------------------|----------------------------------|

| EM78Fx48N | 2.4 ~<br>5.5V | 8K x 15<br>bits   | 304 x<br>8 bits | 40 | 2  | bit<br>1   | 2 ch x<br>10<br>bits | Two wire synchronous communication | Three wire Asynchronous communication | 7 / 10 bits<br>Address &<br>8 bits data | 44 QFP<br>40 DIP<br>28 SKDIP/SOP |

| EM78Fx44N | 2.2 ~<br>5.5V | 4K x 13<br>bits   | 144 x<br>8 bits | 25 | 2  | 1          | 2 ch x<br>10<br>bits | Two wire synchronous communication | Three wire Asynchronous communication | х                                       | 28 SKDIP/SOP<br>24 SKDIP/SOP     |

| EM78Fx42N | 2.2 ~<br>5.5V | 2K x 13<br>bits   | 80 x 8<br>bits  | 18 | 2  | 1          | х                    | х                                  | х                                     | х                                       | 20 DIP/SOP<br>18 DIP/SOP         |

| EM78Fx41N | 2.2 ~<br>5.5V | 1K x 13<br>bits   | 48 x 8<br>bits  | 14 | 1  | 0          | х                    | х                                  | х                                     | х                                       | 16 DIP/SOP<br>10 MSOP            |

## 3 Pin Assignment

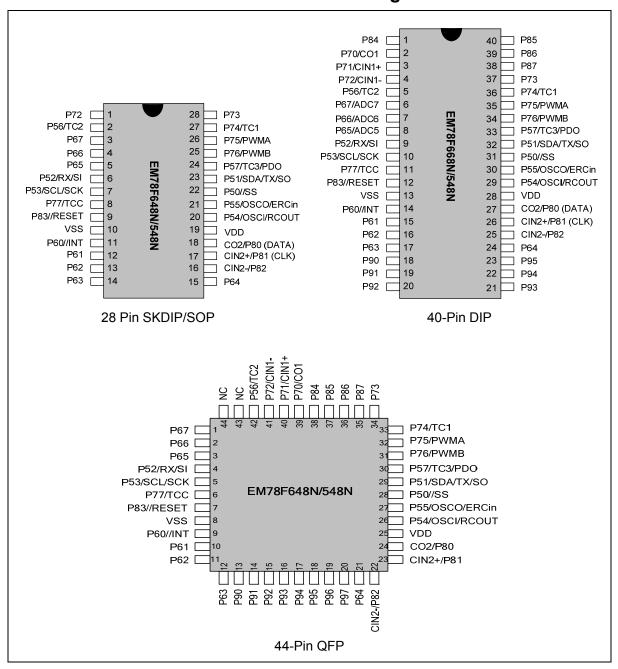

## 3.1 EM78F648N / 548N Pin Assignment

Figure 3-1 EM78F648N / 548N Pin Assignment

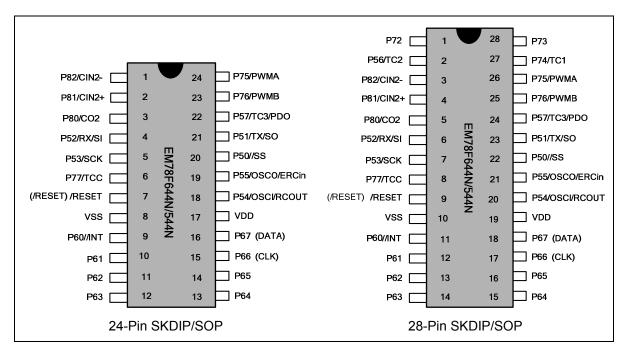

## 3.2 EM78F644N / 544N Pin Assignment

Figure 3-2 EM78F644N / 544N Pin Assignment

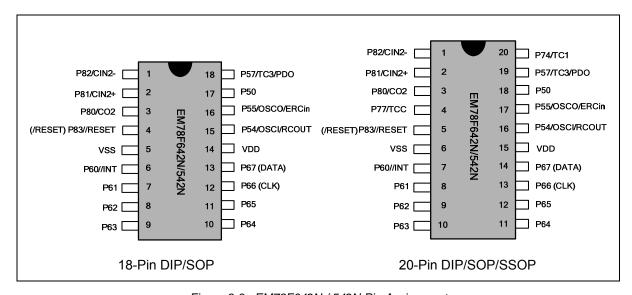

## 3.3 EM78F642N / 542N Pin Assignment

Figure 3-3 EM78F642N / 542N Pin Assignment

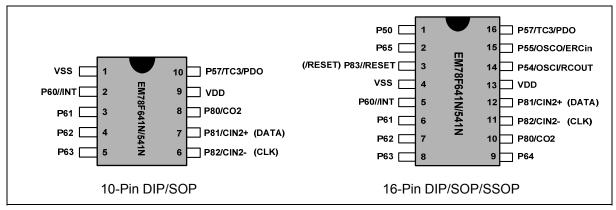

## 3.4 EM78F641N / 541N Pin Assignment

Figure 3-4 EM78F641N / 541N Pin Assignment

## 4 Pin Description

## 4.1 EM78F648N / 548N Pin Description

| Name          | Function | Input<br>Type | Output<br>Type | Description                                                                                         |

|---------------|----------|---------------|----------------|-----------------------------------------------------------------------------------------------------|

| P50//SS       | P50      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive. |

|               | /SS      | ST            |                | SPI slave select pin                                                                                |

|               | P51      |               | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive. |

| P51/SDA/TX/SO | TX       | ST            | CMOS           | UART TX output                                                                                      |

|               | so       |               | CMOS           | SPI serial data output                                                                              |

|               | SDA      | ST            | CMOS           | I2C serial data (open-drain)                                                                        |

|               | P52      | ST            |                | Bidirectional I/O pin with programmable pull-down, opendrain, pull-high, high sink and high drive.  |

| P52/RX/SI     | RX       | ST            | CMOS           | UART RX input                                                                                       |

|               | SI       | ST            |                | SPI serial data input                                                                               |

|               | P53      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive. |

| P53/SCK/SCL   | SCK      | ST            | CMOS           | SPI serial clock input/output                                                                       |

|               | SCL      | ST            | CMOS           | I2C serial clock (open-drain)                                                                       |

## (Continuation)

| (0             | ontinuatior | <u>')</u>     |                |                                                                                                                        |

|----------------|-------------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------|

| Name           | Function    | Input<br>Type | Output<br>Type | Description                                                                                                            |

|                | P54         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

| P54/OSCI/RCOUT | OSCI        |               |                | Clock input of crystal/resonator oscillator                                                                            |

|                | RCOUT       | XTAL          | CMOS           | Clock output of internal RC oscillator<br>Clock output of external RC oscillator (open-drain)                          |

|                | P55         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

| P55/OSCO/ERCin | osco        |               | XTAL           | Clock output of crystal/resonator oscillator                                                                           |

|                | ERCin       | AN            | AIAL           | External RC input pin                                                                                                  |

| P56/TC2        | P56         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

|                | TC2         | ST            |                | Timer 2 clock input                                                                                                    |

|                | P57         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

| P57/TC3/PDO    | TC3         | ST            |                | Timer 3 clock input                                                                                                    |

|                | PDO         | 31            | CMOS           | Programmable divider output                                                                                            |

| P60//INT       | P60         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink, high drive and pin change wakeup. |

|                | /INT        | ST            |                | External interrupt pin                                                                                                 |

| P61~P67        | P61~P67     | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink, high drive and pin change wakeup. |

| P70/CO1        | P70         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

|                | CO1         |               | CMOS           | Output of Comparator 1                                                                                                 |

| P71/CIN1+      | P71         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

|                | CIN1+       | AN            |                | Non-inverting end of Comparator 1                                                                                      |

| P72/CIN1-      | P72         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

|                | CIN1-       | AN            |                | Inverting end of Comparator 1                                                                                          |

| P73            | P73         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

| P74/TC1        | P74         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

|                | TC1         |               | CMOS           | Timer 1 clock input                                                                                                    |

| P75/PWMA       | P75         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

|                | PWMA        |               | CMOS           | PWMA output                                                                                                            |

| P76/PWMB       | P76         | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.                    |

|                | PWMB        |               | CMOS           | PWMB output                                                                                                            |

## (Continuation)

| Name      | Function | Input<br>Type | Output<br>Type | Description                                                                                             |

|-----------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------------|

| P77/TCC   | P77      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-<br>drain, pull-high, high sink and high drive. |

|           | TCC      | ST            |                | Real Time Clock/Counter clock input                                                                     |

| P80/CO2   | P80      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.     |

|           | CO2      |               | CMOS           | Output of Comparator 2                                                                                  |

| (DATA)    | (DATA)   | ST            | CMOS           | DATA pin for Writer programming                                                                         |

| P81/CIN2+ | P81      | ST            |                | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.     |

|           | CIN2+    | AN            | CMOS           | Non-inverting end of Comparator 2                                                                       |

| (CLK)     | (CLK)    | ST            |                | Clock pin for Writer programming                                                                        |

| P82/CIN2- | P82      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.     |

|           | CIN2-    | AN            |                | Inverting end of Comparator 2                                                                           |

| P83/RESET | P83      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.     |

|           | /RESET   | ST            |                | Internal pull-high reset pin                                                                            |

| (/RESET)  | (/RESET) | ST            | CMOS           | /RESET pin for Writer programming                                                                       |

| P84~P87   | P84~P87  | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-<br>drain, pull-high, high sink and high drive. |

| P90~P97   | P90~P97  | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open-drain, pull-high, high sink and high drive.     |

| VDD       | VDD      | Power         | _              | Power                                                                                                   |

| VSS       | VSS      | Power         | -              | Ground                                                                                                  |

Legend: ST: Schmitt Trigger input

XTAL: oscillation pin for crystal/ resonator

AN: analog pin

CMOS: CMOS output

## 4.2 EM78F644N / 544N Pin Description

| Name           | Function | Input<br>Type | Output<br>Type | Description                                                                                     |

|----------------|----------|---------------|----------------|-------------------------------------------------------------------------------------------------|

| P50//SS        | P50      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down                                               |

| P50//SS        | /SS      | ST            | CIVIOS         | SPI slave select pin                                                                            |

|                | P51      |               | CMOS           | Bidirectional I/O pin with programmable pull-down                                               |

| P51/TX/SO      | TX       | ST            | CMOS           | UART TX output                                                                                  |

|                | so       |               | CMOS           | SPI serial data output                                                                          |

|                | P52      | ST            |                | Bidirectional I/O pin with programmable pull-down                                               |

| P52/RX/SI      | RX       | ST            | CMOS           | UART RX input                                                                                   |

|                | SI       | ST            |                | SPI serial data input                                                                           |

| P53/SCK        | P53      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down                                               |

| F55/5CK        | SCK      | ST            | CMOS           | SPI serial clock input/output                                                                   |

|                | P54      | ST            | CMOS           | Bidirectional I/O pin                                                                           |

| P54/OSCI/RCOUT | OSCI     | \/T A         | CIVIOS         | Clock input of crystal/ resonator oscillator                                                    |

|                | RCOUT    | XTAL          | CMOS           | Clock output of internal RC oscillator Clock output of external RC oscillator(open-drain)       |

|                | P55      | ST            | CMOS           | Bidirectional I/O pin                                                                           |

| P55/OSCO/ERCin | osco     | 31            | XTAL           | Clock output of crystal/ resonator oscillator                                                   |

|                | ERCin    | AN            | CMOS           | External RC input pin                                                                           |

| P56/TC2        | P56      | ST            | CMOS           | Bidirectional I/O pin                                                                           |

| F30/1C2        | TC2      | ST            | CIVIOS         | Timer 2 clock input                                                                             |

|                | P57      | ST            | CMOS           | Bidirectional I/O pin                                                                           |

| P57/TC3/PDO    | TC3      | ST            | CIVIOS         | Timer 3 clock input                                                                             |

|                | PDO      | 31            | CMOS           | Programmable divider output                                                                     |

| P60//INT       | P60      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open drain, pull-high and pin change wakeup. |

| 1 00//1141     | /INT     | ST            | OWIGO          | External interrupt pin                                                                          |

| P61~P63        | P61~P63  | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, open drain, pull-high and pin change wakeup. |

| P64~P65        | P64~P65  | ST            | CMOS           | Bidirectional I/O pin with programmable open-drain, pullhigh and pin change wakeup.             |

| P66            | P66      | ST            | CMOS           | Bidirectional I/O pin with programmable open-drain, pull-high and pin change wakeup.            |

| (CLK)          | (CLK)    | ST            |                | Clock pin for Writer programming                                                                |

| P67            | P67      | ST            | CMOS           | Bidirectional I/O pin with programmable open-drain, pullhigh and pin change wakeup.             |

| (DATA)         | (DATA)   | ST            | CMOS           | Data pin for Writer programming                                                                 |

## (Continuation)

| Name      | Function | Input<br>Type | Output<br>Type        | Description                                                      |

|-----------|----------|---------------|-----------------------|------------------------------------------------------------------|

| P72 ~ P73 | P72~P73  | ST            | CMOS                  | Bidirectional I/O pin with programmable pull-down and pull-high. |

| P74/TC1   | P74      | ST            | CMOS                  | Bidirectional I/O pin with programmable pull-down and pull-high. |

|           | TC1      |               | CMOS                  | Timer 1 clock input                                              |

| P75/PWMA  | P75      | ST            | CMOS                  | Bidirectional I/O pin with programmable pull-down and pull-high. |

|           | PWMA     |               | CMOS                  | PWMA output                                                      |

| P76/PWMB  | P76      | ST            | CMOS                  | Bidirectional I/O pin with programmable pull-down and pull-high. |

|           | PWMB     |               | CMOS                  | PWMB output                                                      |

| P77/TCC   | P77      | ST            | CMOS                  | Bidirectional I/O pin with programmable pull-down and pull-high. |

|           | TCC      | ST            |                       | Real Time Clock/Counter clock input                              |

|           |          | CMOS          | Bidirectional I/O pin |                                                                  |

| P80/CO2   | CO2      | ST            | CMOS                  | Bidirectional I/O pin with programmable pull-down and pull-high. |

| P81/CIN2+ | P81      | ST            | CMOS                  | Bidirectional I/O pin                                            |

| FOI/CINZ+ | CIN2+    | AN            | CIVIOS                | Non-Inverting end of Comparator 2                                |

| P82/CIN2- | P82      | ST            | CMOS                  | Bidirectional I/O pin                                            |

| FOZ/CINZ- | CIN2-    | AN            | CIVIOS                | Inverting end of Comparator 2                                    |

| /RESET    | /RESET   | ST            | CMOS                  | Internal pull-high reset pin                                     |

| (/RESET)  | (/RESET) | ST            | CIVIOS                | /RESET pin for Writer programming                                |

| VDD       | VDD      | Power         | _                     | Power                                                            |

| VSS       | VSS      | Power         | -                     | Ground                                                           |

Legend: ST: Schmitt Trigger input

XTAL: oscillation pin for crystal / resonator

AN: analog pin

CMOS: CMOS output

## 4.3 EM78F642N / 542N Pin Description

| Name            | Function | Input<br>Type | Output<br>Type | Description                                                                                    |

|-----------------|----------|---------------|----------------|------------------------------------------------------------------------------------------------|

| P50             | P50      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down                                              |

|                 | P54      | ST            | CMOS           | Bidirectional I/O pin                                                                          |

| P54/OSCI/RCOUT  | OSCI     |               | CIVIOS         | Clock input of crystal/resonator oscillator                                                    |

|                 | RCOUT    | XTAL          | CMOS           | Clock output of internal RC oscillator<br>Clock output of external RC oscillator (open-drain)  |

|                 | P55      | ST            | CMOS           | Bidirectional I/O pin                                                                          |

| P55/OSCO/ERCin  | osco     | 5             | XTAL           | Clock output of crystal / resonator oscillator                                                 |

|                 | ERCin    | AN            | CMOS           | External RC input pin                                                                          |

|                 | P57      | ST            |                | Bidirectional I/O pin                                                                          |

| P57/TC3/PDO     | TC3      | ST            | CMOS           | Timer 3 clock input                                                                            |

|                 | PDO      | 31            |                | Programmable divider output                                                                    |

| P60//INT        | P60      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, opendrain, pull-high and pin change wakeup. |

|                 | /INT     | ST            |                | External interrupt pin                                                                         |

| P61~P63         | P61~P63  | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down, opendrain, pull-high and pin change wakeup. |

| P64~P65         | P64~P65  | ST            | CMOS           | Bidirectional I/O pin with programmable open-drain, pullhigh and pin change wakeup.            |

| P66             | P66      | ST            | CMOS           | Bidirectional I/O pin with programmable open-drain, pullhigh and pin change wakeup.            |

| (CLK)           | (CLK)    | ST            |                | Clock pin for Writer programming                                                               |

| P67             | P67      | ST            | CMOS           | Bidirectional I/O pin with programmable open-drain and pull-high.                              |

| (DATA)          | (DATA)   | ST            | CMOS           | Data pin for Writer programming                                                                |

| P74/TC1         | P74      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down and pull-high.                               |

|                 | TC1      |               | CMOS           | Timer 1 clock input                                                                            |

| P77/TCC         | P77      | ST            | CMOS           | Bidirectional I/O pin with programmable pull-down and pull-high.                               |

|                 | TCC      | ST            |                | Real Time Clock/Counter clock input                                                            |

| P80/CO2         | P80      | ST            | CMOS           | Bidirectional I/O pin                                                                          |

| 1 00/002        | CO2      | O1            | CMOS           | Output of Comparator 2                                                                         |

| P81/CIN2+       | P81      | ST            | CMOS           | Bidirectional I/O pin                                                                          |

| 1 0 1/0 11 12 1 | CIN2+    | AN            | CIVICO         | Non-inverting end of Comparator 2                                                              |